僅5,000行Verilog代碼的RISC-V內核,支持Linux,性能接近486

2020-02-20 14:59:45 EETOP

東京工業大學計算機學院的一個團隊中開發了一種可移植且具有Linux功能的RISC-V片上系統(SoC),僅用5,000行Verilog代碼即可實現。

“ RISC-V是一種開放的,免版稅的指令集架構,已在加利福尼亞大學伯克利分校開發。使用RISC-V的處理器可以自由設計和發布,”該團隊在背景技術中解釋道。“因此,到目前為止,已經發布了各種處理器內核和片上系統(SoC)。但是,有一些便攜式的RISC-V公共計算機系統可以運行Linux操作系統。

“在本文中,我們以Verilog HDL設計了針對FPGA的可移植的支持Linux的RISC-V片上系統(SoC)。該系統可以在具有較少硬件資源的FPGA上實現,并可以在低成本FPGA上實現。”

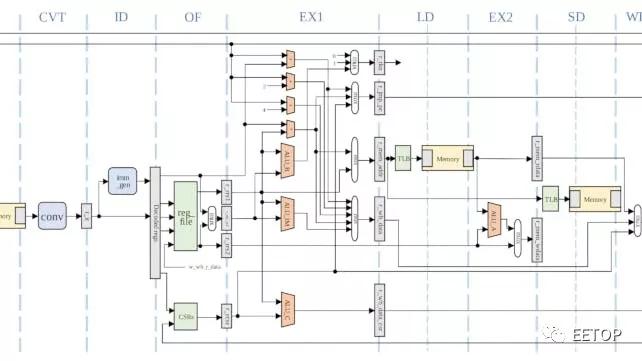

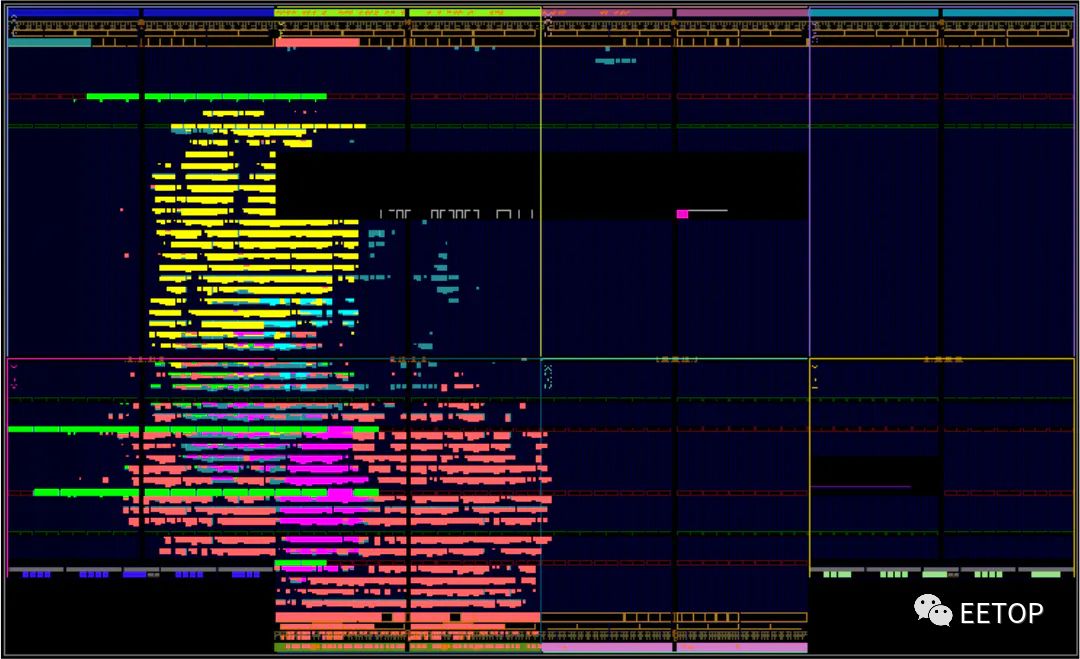

RVSoC占用了非常少的FPGA資源

最終的設計被稱為RVSoC,它實現了32位RV32IMAC指令集體系結構,并提供了帶有內存管理單元(MMU)的12級流水線-對于引導Linux并非嚴格要求,因為內核在事件中支持手動內存映射沒有可用的硬件MMU,但除了最基本的可能用途之外,它絕對是所有其他產品的必備品。盡管如此,該設計僅以5,000行Verilog HDL出現。

團隊承諾:“我們計劃發布設計的RVSoC的RTL代碼,作為一種開放且免版稅的RTL設計。” “由于RVSoC是一種支持Linux并使用少量硬件資源的系統,因此可以應用于各種用途。RISC-V的一個特點是它為計算機系統開發人員提供了擴展指令的空間。擴展性可能是特定于應用程序的加速器的基本要求,并且可以實現更專業的指令集。

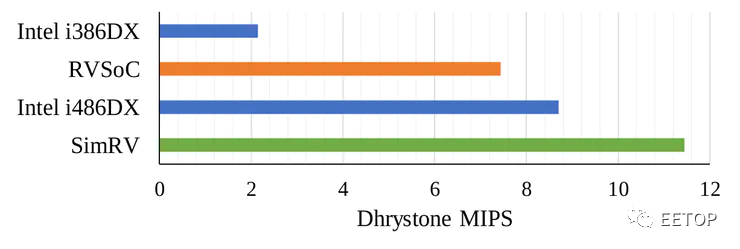

RVSoC的性能介于386和486處理器之間

RVSoC的性能介于386和486處理器之間

“通過添加獨特的指令以及相關軟件的開發,節省資源的RVSoC可以適用于各種加速器和特殊處理器內核的實現。RVSoC的Verilog HDL代碼中的行數約為5,000,并且相對而言易于理解具有Linux功能的計算機系統的整個實現。因此,它適合用作計算機科學教育的示例計算機系統。”

該論文將在IEICE信息與系統交易雜志上發表。

論文下載

首先請在朋友圈或微信群分享此文,然后點擊閱讀原文進入EETOP公眾號,后臺發送消息:risc-v pdf,可獲取下載鏈接。(注:前幾天已分享過改論文)