NoC IP如何借助人工智能和機器學(xué)習(xí)滿足SoC設(shè)計需求?

2025-04-10 12:10:01 EETOP拓?fù)渖蓵r間從20小時縮短至4小時(提升了5倍)

初始優(yōu)化時間從3小時壓縮至10分鐘(快了18倍)

最終的物理感知調(diào)整時間則從兩周縮短至僅100分鐘(提速約20倍)

除了效率提升,F(xiàn)lexGen將布線長度減少了高達(dá)30%,并將延遲降低了10%,為復(fù)雜SoC及芯粒設(shè)計開辟高效路徑。

—Arteris總裁兼首席執(zhí)行官

K. Charles Janac

1FlexGen 的開發(fā)得益于哪些技術(shù)突破?

機器學(xué)習(xí)或 AI 算法在其中發(fā)揮了作用嗎?

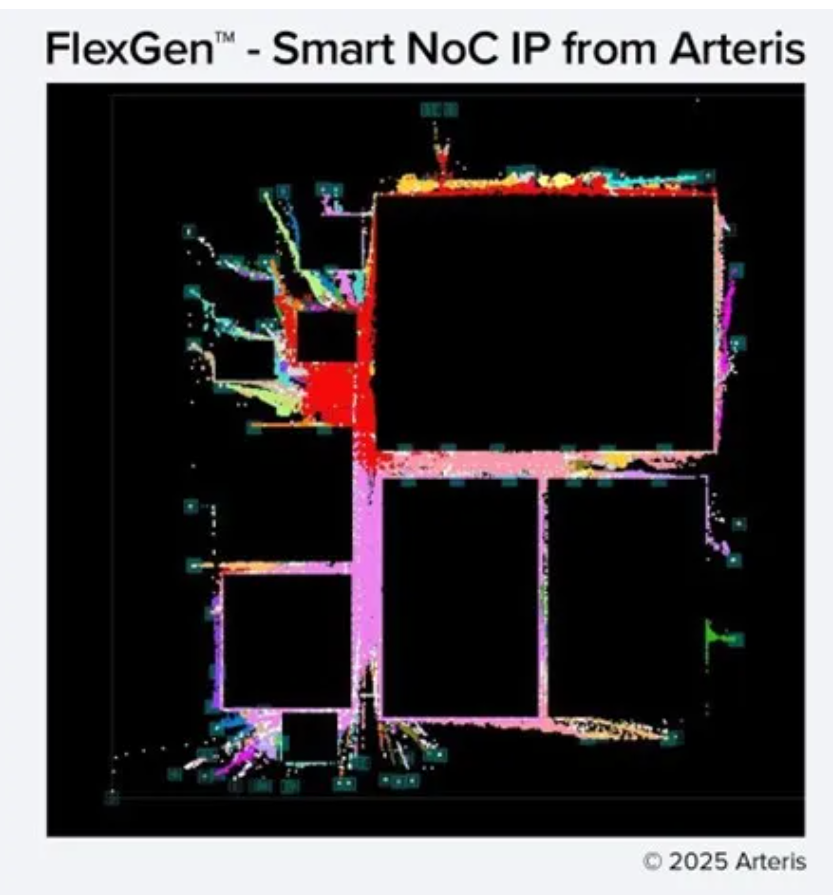

FlexGen 借助人工智能(AI)與機器學(xué)習(xí)(ML)的技術(shù)進步,實現(xiàn)了片上網(wǎng)絡(luò)(NoC)設(shè)計流程的自動化,大幅減少了傳統(tǒng)半導(dǎo)體芯片 SoC 設(shè)計中的耗時環(huán)節(jié)。通過基于機器學(xué)習(xí)的啟發(fā)式算法,F(xiàn)lexGen 可以智能地探索設(shè)計方案并優(yōu)化 NoC 拓?fù)浣Y(jié)構(gòu),從而將布線長度縮短高達(dá) 30%,延遲降低高達(dá) 10%。這些創(chuàng)新對提升能效、達(dá)成更優(yōu)的功耗、性能、面積(PPA)指標(biāo)至關(guān)重要。

2FlexGen 如何使 NoC 成為 SoC 或其他芯片中互聯(lián)的選擇?

NoC 不是SoC的替代品,它是能成功把上百個 IP 連接起來組成 SoC 的一種互連。可顯著優(yōu)化功耗、性能與面積(PPA)。FlexGen 的突破性在于:傳統(tǒng)流程中手動實現(xiàn)單一NoC拓?fù)涞臅r間,現(xiàn)在可用來探索數(shù)十種 SoC 架構(gòu)設(shè)計方案。

FlexGen 完整保留了 FlexNoC 非一致性 NoC IP 的手動編輯與驗證功能,因此其自動化生成的結(jié)果可以根據(jù)需要手動編輯。FlexGen 的高級智能啟發(fā)式算法可以選擇性地逐步使用:既可在自動化設(shè)計基礎(chǔ)上進行手動修改,也能在人工搭建的基礎(chǔ) NoC上構(gòu)建自動化拓?fù)洹?/span>

該技術(shù)是完全可重復(fù)的,這意味著相同的輸入將產(chǎn)生相同的輸出,從而簡化了后期規(guī)范更改的實現(xiàn),大幅提升了效率。

3FlexGen能否更好地支持Multi-die配置,如芯粒(Chiplet)?

FlexGen 繼承并擴展了 Arteris 經(jīng)過驗證的芯粒技術(shù)能力,支持具有高性能、非一致性 NoC的 Multi-die 架構(gòu)。FlexGen 的自動化設(shè)計能力、物理感知特性以及對異構(gòu)集成的支持,使其成為推動芯粒設(shè)計創(chuàng)新的理想選擇。

4NoC如何幫助實現(xiàn)設(shè)計周期早期的測試驗證?

FlexGen 能夠自動生成在邏輯設(shè)計層面正確的 NoC 架構(gòu),嚴(yán)格滿足所有指定的互連參數(shù)(包括數(shù)據(jù)位寬、時鐘頻率和內(nèi)存映射)和性能要求。此外,F(xiàn)lexGen 內(nèi)置的物理感知能力使其能夠利用 SoC 布局,在長信號線中重需要的地方插入流水線,以促進后端設(shè)計的時序收斂。

5FlexGen 適用于哪些應(yīng)用場景?

FlexGen 非常適合對可擴展性能和 PPA 優(yōu)化有高要求的復(fù)雜SoC設(shè)計,主要包括五大領(lǐng)域:

AI與機器學(xué)習(xí) SoC:顯著提升推理/訓(xùn)練工作負(fù)載處理能力。

汽車電子(ADAS)SoC:通過復(fù)雜流量管理支撐高級駕駛輔助系統(tǒng)。

5G/6G 通信 SoC:實現(xiàn)超低延遲和高帶寬系統(tǒng)。

消費電子 SoC:為智能設(shè)備提供高能效芯片方案。

工業(yè)物聯(lián)網(wǎng) SoC:優(yōu)化連接和自動化系統(tǒng)的整體性能。

如需了解更多信息, 請點擊“下方二維碼”索取 FlexGen 產(chǎn)品手冊:

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章