臺積電工程師稱最近將 2nm 良率提高了 6%,為客戶節(jié)省數十億美元

2024-12-04 12:18:38 EETOP臺積電計劃在明年下半年開始使用其N2(2納米級)制程技術進行半導體的量產,目前公司正全力優(yōu)化這項技術,包括降低工藝中的變異性和缺陷密度,從而提高良率。一位臺積電員工最近表示,團隊已經成功將測試芯片的良率提升了6%,為客戶節(jié)省了“數十億美元”的成本。

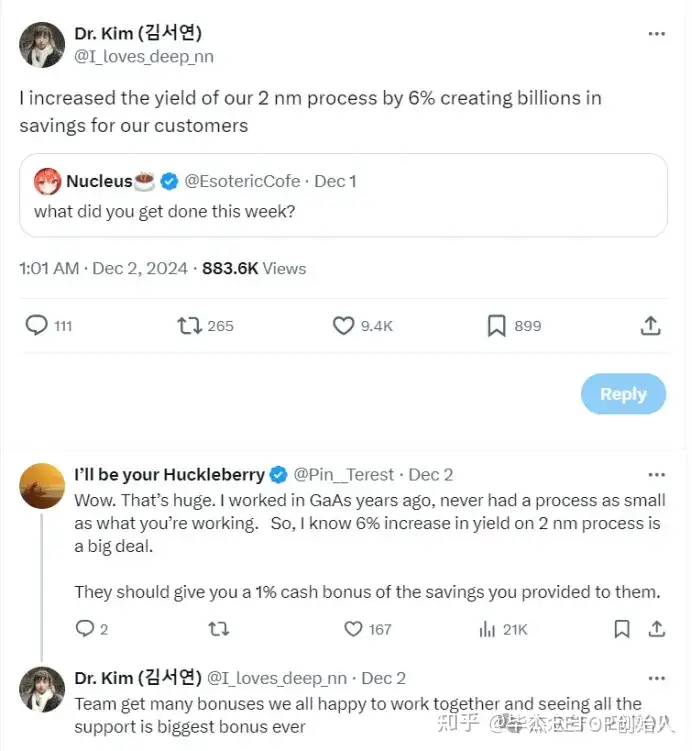

X 平臺網友Dr. Kim(@I_loves_deep_nn)自稱是臺積電員工,但未透露改善的是 SRAM 測試芯片還是邏輯測試芯片的良率。外媒Tot's Hardware認為,臺積電明年1月才開始提供2納米技術的shuttle測試晶圓服務,現在不太可能改善2納米制造最終實際芯片原型的良率。

提升SRAM和邏輯測試芯片的良率至關重要,因為這最終可以顯著降低客戶成本。客戶支付晶圓費用,因此更高的良率直接關系到他們的經濟效益。

臺積電的N2將是其首個使用全環(huán)繞柵極(GAA)納米片晶體管的工藝,這種技術能夠大幅降低功耗、提高性能并增加晶體管密度。特別是,與3納米FinFET晶體管相比,臺積電的GAA納米片晶體管不僅更小,還通過提供更好的靜電控制和減少漏電,在不犧牲性能的情況下支持更小的高密度SRAM單元。其設計增強了閾值電壓調節(jié)能力,確保可靠運行,并支持邏輯晶體管和SRAM單元的進一步微型化。然而,臺積電需要掌握如何在合理良率下生產這種全新的晶體管。

采用N2制程技術制造的芯片,預計在相同晶體管數量和頻率下,功耗比N3E制程制造的芯片降低25%至30%;在相同晶體管數量和功耗下,性能提升10%至15%;在速度和功耗相當的情況下,晶體管密度提升15%。

臺積電預計將在2025年下半年(可能是2025年底)開始N2工藝的芯片量產。為此,這家全球最大的芯片代工廠還有充足的時間來進一步提高良率和降低缺陷密度。

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導體創(chuàng)芯網 快訊

相關文章