銅互連挺進2nm!

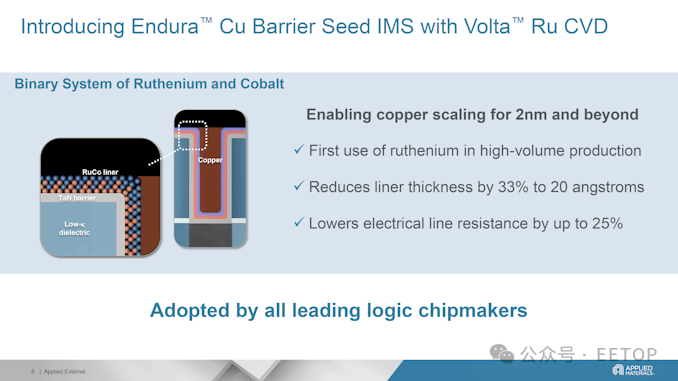

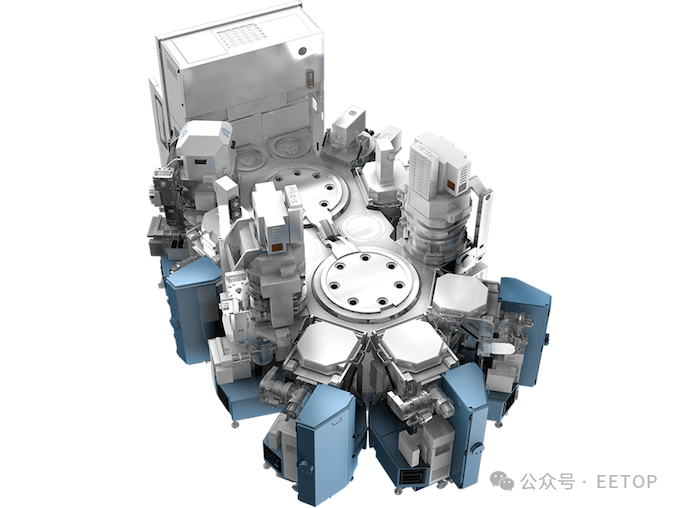

2024-07-13 12:24:21 anandtech盡管在過去的十年里,摩爾定律的進展顯然有所放緩,但每一代新的工藝技術仍在提升晶體管的密度。然而,向更小的晶體管供電面臨挑戰,因為更小的晶體管意味著芯片內的電源線更細,這增加了它們的電阻,可能導致成品率下降。為了解決這一問題,本周應用材料公司推出了新的Applied Endura Copper Barrier Seed IMS和Volta Ruthenium Copper Vapor Deposition (CVD)工具,使芯片制造商能夠在2nm級及更先進的工藝技術中繼續使用銅線。

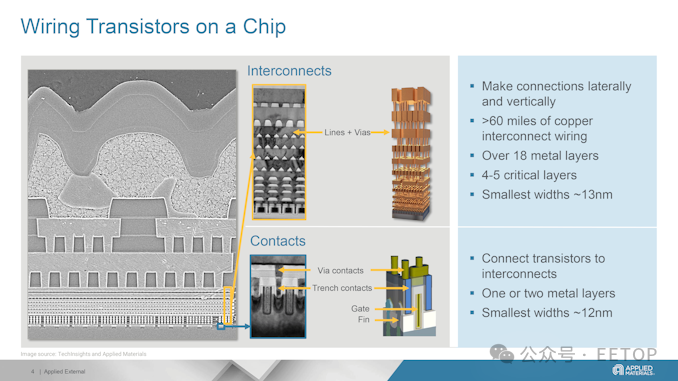

當今先進的邏輯處理器大約有20層金屬層,包含細信號線和較粗的電源線。隨著晶體管的縮小,縮小布線帶來了諸多挑戰。較細的布線具有更高的電阻,而較近的布線則增加了電容和電氣串擾。兩者的結合會導致功耗增加,同時限制性能提升,這對于希望在數據中心處理器中兼顧一切的處理器尤為棘手。將電源軌轉移到晶圓的背面預計可以通過減少布線復雜性并騰出更多空間給晶體管,從而提升性能和效率。

然而,背面供電網絡(BSPDN)并不能完全解決細線問題。隨著光刻縮放的進展,晶體管特征和布線溝槽都變得更小。這意味著障礙層和襯墊在這些溝槽中占據了更多空間,導致沒有足夠的空間在不產生空隙的情況下沉積銅,從而增加電阻并降低成品率。此外,電線更近也會使低k電介質變薄,使其在蝕刻過程中更容易受損。這種損傷會增加電容,削弱芯片,使其不適合3D堆疊。因此,隨著行業的發展,銅布線面臨顯著的物理縮放挑戰,但應用材料公司提出了新的解決方案。

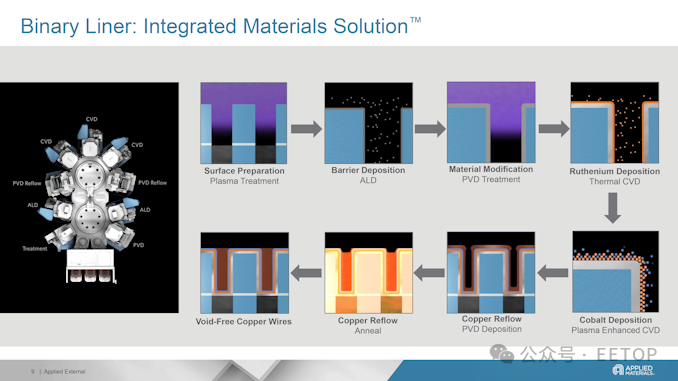

當代制造技術使用回流焊來填充銅的互連,其中退火過程有助于銅從晶圓表面流入布線溝和通孔。這個過程取決于銅流動的襯里。通常,使用CVD鈷膜作為內襯,但這種膜對于3nm級節點來說太厚了(會影響電阻和成品率)。

應用材料公司建議使用厚度低于 20A(2nm,20 埃)的釕鈷 (RuCo) 二元襯里,這將為銅回流焊提供更好的表面性能。這最終將允許為無空隙導電銅的回流焊增加 33% 的空間,從而將整體電阻降低 25%。雖然使用新襯墊需要新的工具,但它可以實現更好的互連,這意味著更高的性能、更低的功耗和更高的成品率。

應用材料公司表示,截至目前,其新的Endura Copper Barrier Seed IMS和Volta Ruthenium CVD工具已被所有主要邏輯制造商采用,包括臺積電和三星代工的3nm級節點及更先進節點。

臺積電執行副總裁兼聯席首席運營官Y.J. Mii博士表示:“半導體行業必須大幅提高能效性能,以實現人工智能計算的可持續增長。降低互連電阻的新材料將在半導體行業發揮重要作用,同時其他創新將提高整體系統性能和功耗。

但是,薄而高效的襯里并不是 3nm 及以后生產節點布線的唯一關鍵因素。布線溝槽不僅采用 Co/RuCo 襯里和 Ta/N 屏障,還采用低介電常數 (Low-K) 薄膜,以最大限度地減少電荷積聚、降低功耗并降低信號干擾。自 2000 年代初以來,應用材料公司一直提供其 Black Diamond Low-K 薄膜。

但新的生產節點需要更好的電介質,因此本周應用材料公司推出了升級版的Black Diamond材料和等離子增強化學氣相沉積(PEVCD)工具,即Producer Black Diamond PECVD系列。這種新材料通過進一步降低介電常數,同時增加芯片的機械強度,使其能夠縮放到2nm及更小節點,這對于邏輯和存儲的3D堆疊非常有利。應用材料公司表示,新的Black Diamond正被主要邏輯和DRAM芯片制造商迅速采用。

應用材料公司半導體產品事業部總裁Prabu Raja博士表示:“人工智能時代需要更節能的計算,芯片布線和堆疊對性能和功耗至關重要。應用材料公司最新的集成材料解決方案使業界能夠將低電阻銅線擴展到新興的埃米節點,而我們最新的低介電常數介電材料可同時降低電容并增強芯片,將 3D 堆疊提升到新的高度。”

本文由EETOP編譯自anandtech