2nm工藝新突破!家用微波爐“烹”出下一代芯片!

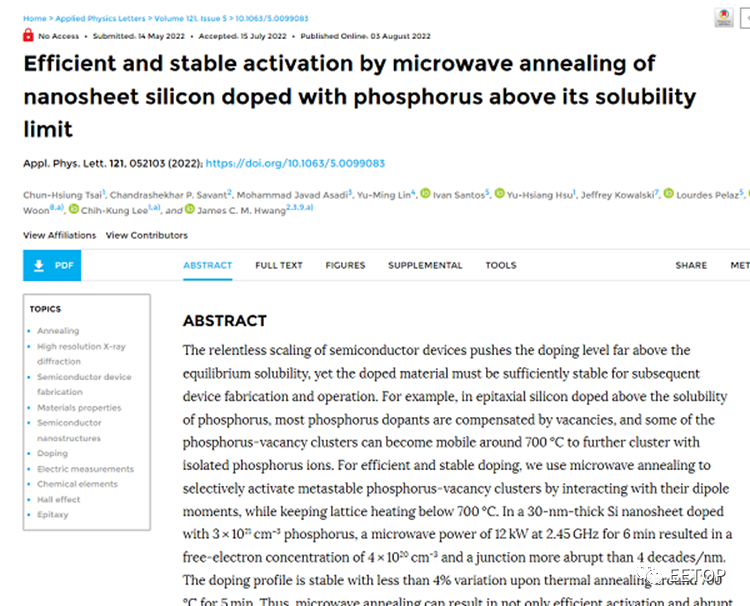

2022-09-12 14:14:05 EETOP為了使半導體工藝繼續縮小,硅必須摻雜越來越高的磷濃度,以促進準確和穩定的電流傳輸。就目前而言,隨著業界開始大規模生產 3nm芯片,傳統的退火方法仍然有效。然而,隨著業界達到 3nm 以上,需要確保高于其在硅中的平衡溶解度的磷濃度。除了實現更高的濃度水平外,一致性對于制造功能性半導體材料至關重要。

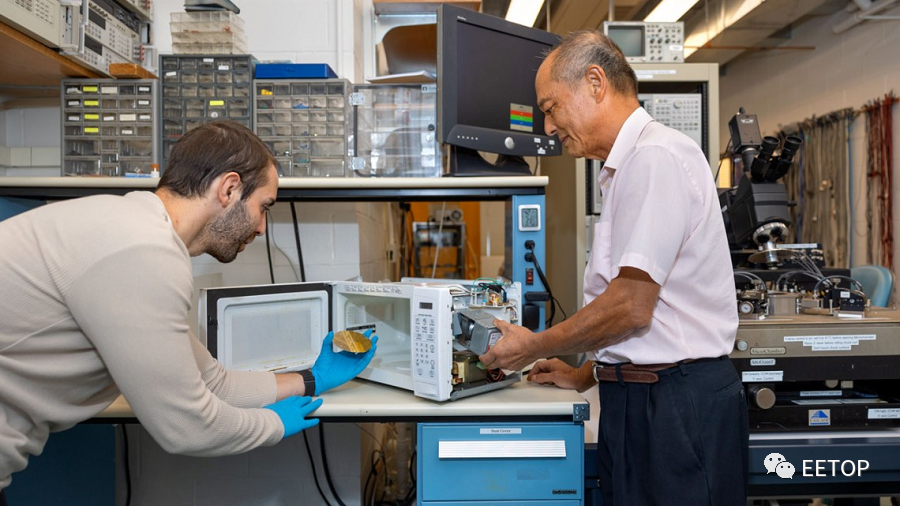

美國康奈爾大學的科學家們一直在使用改進的家用微波爐來幫助克服實際2nm 半導體生產的重大障礙。由此產生的微波退火爐借鑒了臺積電關于微波和硅摻雜磷的理論。因此,半導體制造商可以使用新設計的設備和技術突破以前的磷濃度限制。

據康奈爾大學官網報道,該大學工程學教授改裝的家用微波爐正在幫助“烹飪”下一代手機、計算機和其他電子產品,因為這項發明被證明可以克服半導體行業面臨的重大挑戰。

不久前發表在 Applied Physics Letters上的一篇論文詳細介紹了這項研究。第一作者為康奈爾大學材料科學與工程系研究教授James Hwang ;康奈爾大學的其他貢獻者是博士生 Chandrasekhar Savant 和前博士后研究員 Mohammed Javad Asadi。

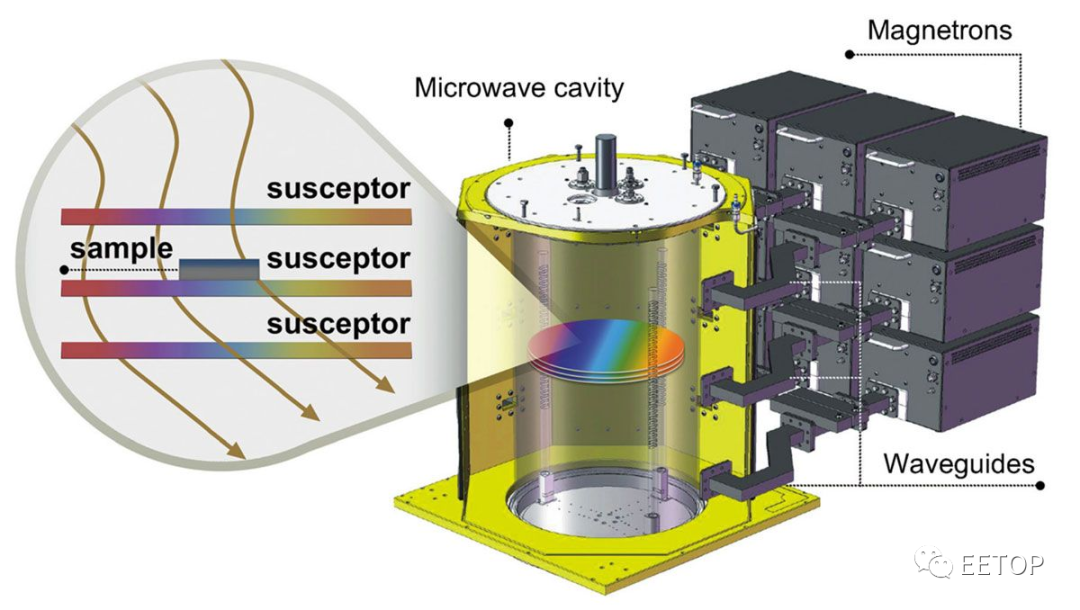

臺積電此前曾推測,微波可用于退火(加熱)過程,以促進增加磷的摻雜濃度。然而,以前的微波加熱源往往會產生駐波,這不利于加熱的一致性。簡單來說,以前的微波退火設備加熱其內容物不均勻。

康奈爾大學的科學家得到臺積電的支持,開展微波退火研究。在本周早些時候由康奈爾大學分享的由此產生的科學論文中,科學家們得出結論,由于他們先進的微波退火方法,他們已經“克服了高于溶解度的高而穩定摻雜的基本挑戰”。

Hwang 說,這一發現可用于生產 2025 年左右出現的半導體材料和電子產品,他已與博士后研究員 Gianluca Fabi 為原型微波退火器申請了兩項專利。

“一些制造商目前正在生產 3 納米的半導體材料”Hwang 說。“這種新的微波方法有可能使臺積電和三星等領先制造商的尺寸縮小到僅 2 納米。”

這一突破可能會改變微芯片中使用的晶體管的幾何形狀。20 多年來,晶體管被制成像背鰭一樣豎立起來,以便在每個微芯片上封裝更多,但制造商最近開始試驗一種新架構,其中晶體管作為納米片水平堆疊,可以進一步增加晶體管的密度和控制。通過微波退火實現的過度摻雜材料將是新架構的關鍵。

第一作者簡介:

James Hwang 畢業于康奈爾大學材料科學與工程系,獲得博士學位。在 IBM、貝爾實驗室、通用電氣和 GAIN 擁有多年的行業經驗后,他的大部分學術生涯都在利哈伊大學度過。他共同創立了 GAIN 和 QED;后者成為上市公司 IQE。他曾是美國空軍GHz-THz電子科學研究辦公室的項目官員。他曾在美國康奈爾大學、意大利馬爾凱理工大學、新加坡南洋理工大學、臺灣國立交通大學和中國上海交通大學擔任客座教授。他是 IEEE Life Fellow 和杰出的微波講師。他發表了大約 400 篇參考技術論文,并獲得了 8 項美國專利。他研究電子、光學和微機電設備和電路。他目前的研究興趣包括掃描微波顯微鏡、二維原子層材料和器件,以及用于單個生物細胞的電磁傳感器。