突破天花板!存儲密度一下提高40%!不采用EUV的美光最新1α納米DRAM是如何做到的?

2021-01-28 13:13:56 EETOP美光聲稱通過一種新工藝打破了1z DRAM節點的天花板,該工藝將存儲密度提高了40%!

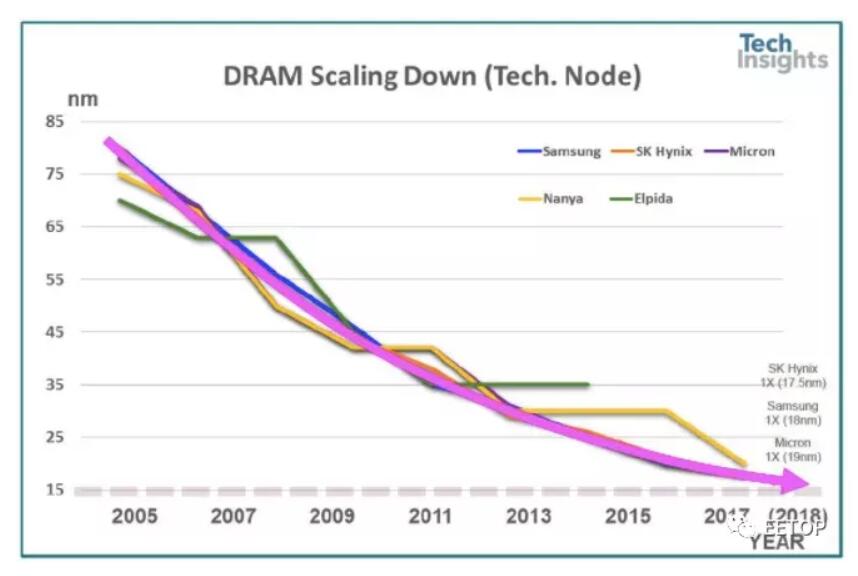

DRAM的縮小速度明顯慢于許多其他芯片。雖然微處理器的工藝已經到了5nm節點,但DRAM仍然停留在20nm和10nm節點之間,并且從2016年左右開始就一直如此。理論上,10nm是DRAM的極限。

正因為如此,制造商們創造了一種新的工藝節點命名方案,它指的是存儲單元陣列中有效區域間距的一半的尺寸。慣例如下。

1x nm:19nm–17nm(Gen1)

1y nm:16nm–14nm(第2代)

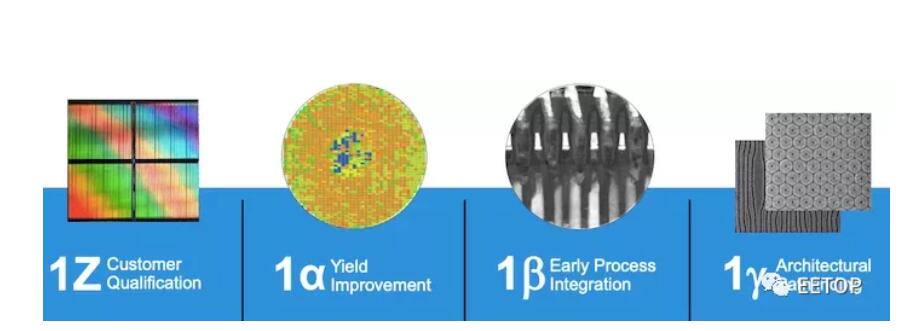

目前,廠商只達到了1z的 "節點"。不過現在,美光科技已經成為第一家將下一個最小維度的DRAM--1α推向市場的公司。

電容器縱橫比和DRAM縮放

出于多種原因,提高DRAM工藝制程并不如像微處理器那么簡單。

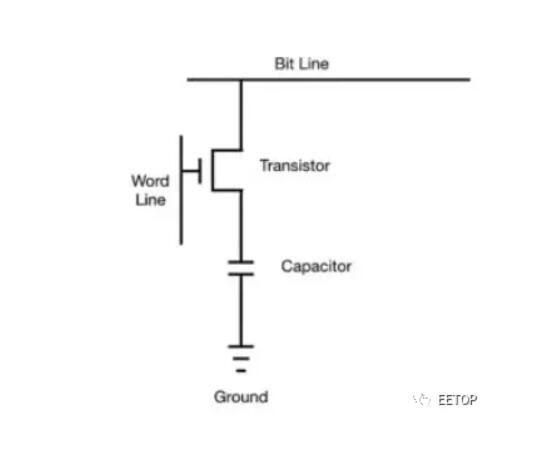

單個DRAM單元由傳輸晶體管和存儲電容器組成。

原因之一涉及DRAM的本質。它需要一個存儲電容器來保存數值。由于設備的電容大小直接與其物理尺寸有關,因此橫向縮小電容器會降低其容量。電容器不僅不再能夠容納可測量的電荷,而且還會更快地泄漏電荷,從而需要更多的動態刷新,這樣反而提高了功耗。

一些行業供應商認為,要充分克服這一挑戰,必須大力發展新材料。

制造的挑戰

使DRAM進一步縮放的另一個限制因素涉及制造方面的挑戰。

硅加工通常依靠光刻技術將詳細的圖案蝕刻到半導體硅片上。DRAM單元的光刻設計要求,特別是電容器的復雜性,使得制造工藝更加困難。

美光DRAM路線圖

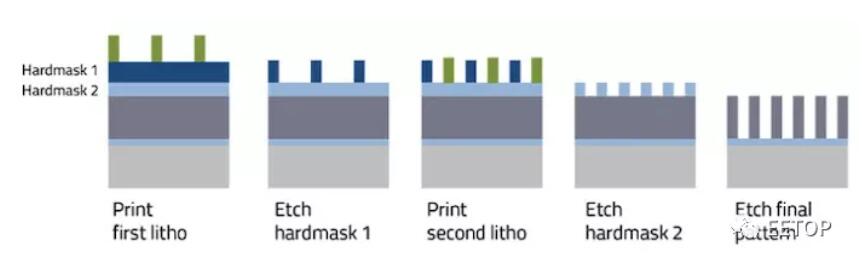

隨著特征的縮小,光刻受到瑞利準則(Rayleigh)的限制。該標準指出,不可能使用光刻來蝕刻小于所用光波長的大約一半的特征。這意味著,當特征被蝕刻得足夠小時,使用常規技術幾乎不可能創建足夠精確的DRAM單元。

一些挑戰包括以良好的對齊方式設計電容孔,以及為可預測的行為創造具有精確長寬比的電容。

內存密度提高40%

考慮到美光的新型1αDRAM與先前的1z DRAM節點相比,其存儲密度提高了40%,因此這一消息對于存儲空間意義重大。美光還聲稱,與1z移動DRAM相比,這項新技術可節省多達15%的功耗。

據該公司介紹,1α節點將在今年應用在其DRAM產品系列中,以支持目前所有使用DRAM的環境。

不采用EUV,美光推出新的內存處理節點

盡管這些挑戰使進度驚人地緩慢,但一些供應商仍在進步。美光公司是第一家近期取得重大進展的公司,成為第一家將1α工藝節點投入量產的公司。

與某些尋求極端紫外線(EUV)光刻技術作為解決方案的公司不同,美光通過“多重圖案化”實現了縮小尺寸。該技術背后的思想是通過添加非光刻步驟以從單個較大的特征中創建多個小的特征來提高分辨率。

美光的接下來的三個DRAM節點將繼續使用深紫外線(DUV)光刻技術,但該公司現在正在考慮將EUV用于其1