伺服環路ADC測試簡介

2023-10-19 11:15:00 EETOP編譯A/D 轉換器 (ADC) 的靜態參數有助于了解直流或緩慢變化信號的器件行為。然而,為了確定靜態參數(包括失調和增益誤差、微分非線性(DNL) 和積分非線性(INL)),我們首先需要確定 ADC 的直流傳遞函數。伺服環路測試是確定 ADC 傳遞函數的經典工業方法。

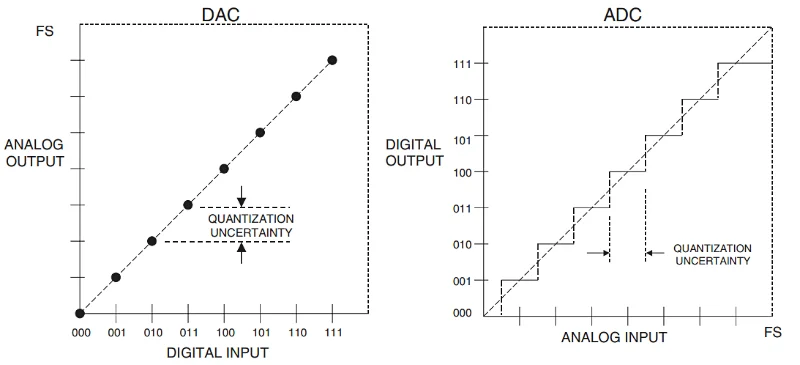

測試 ADC 可能比測試 D/A 轉換器 (DAC) 困難得多。這是因為 DAC 傳輸曲線是一對一映射函數,而 ADC 特性曲線是多對一映射函數。圖 1 對此進行了說明。

圖1顯示了3bit單極性DAC和3bit單極性ADC的理想特性曲線。對于DAC來說,輸入和輸出都是量化的,傳遞函數由八個點組成。作為一對一的映射函數,我們可以輕松測量每個數字代碼的 DAC 輸出電壓并確定其傳輸曲線。另一方面,給定的 ADC 輸出代碼對應于連續范圍的輸入值。因此,我們無法通過向 ADC 輸入施加已知電壓并測量輸出代碼來確定 ADC 傳遞函數。

為了完全確定 ADC 轉換曲線,我們必須測量其代碼轉換點。這使得 ADC 測試變得復雜且昂貴。事實上, ADC 單位售價的大約15% 到 20%是由于不同的測試造成的。學術界和工業界的研究人員進行了大量研究,尋找有效的 ADC 測試方法。一種流行的方法是伺服環路測試,如下所述。

伺服環路測試于 1975 年首次推出,是一種基于反饋的技術,用于確定 ADC 轉換點。測試裝置的基本配置如圖 2 所示。

反饋環路由數字比較器、兩個電流源(I 1 和 I 2)、配置為模擬積分器的運算放大器以及被測 ADC 組成。為了確定給定的轉換點,將相應的代碼應用于比較器的“A”輸入。該值與 ADC輸出代碼進行比較(ADC 輸出連接到比較器的另一個輸入“B”)。如果 ADC輸出大于目標代碼 (B > A),比較器將打開上部開關一段特定的時間段 Δt。當 I 1 流經 C 1時,積分器輸出減少:

因此,這會減少 ADC 輸出代碼,使其更接近應用于比較器“A”輸入的目標代碼。這一過程將持續進行,直到 ADC 輸入距離目標轉換點在一步 (ΔV) 以內。在下一個周期,ADC 輸入又減少了 ΔV,使得 ADC 輸出小于或等于 A (B ≤ A)。此時,比較器打開下部開關并增加積分器輸出:

RFhib1CEchQxA/640?wx_fmt=png" data-type="png" data-w="162" data-index="5" src="http://www.xebio.com.cn/uploadfile/2023/1019/20231019111639968.jpg" _width="162px" crossorigin="anonymous" alt="圖片" data-fail="0" style=";padding: 0px;outline: 0px;max-width: 100%;box-sizing: border-box !important;overflow-wrap: break-word !important;vertical-align: bottom;height: auto !important;width: 162px !important;visibility: visible !important"/>

通常,兩個電流源具有相同的值;因此,任一方向的步長是相同的。由于 ADC輸入距離轉換點僅一步之遙,后續步驟將使 ADC 輸入在每個周期跨越轉換點。換句話說,ADC 將交替輸出大于 A (B < A) 或小于或等于 A (B ≤ A) 的代碼序列。

圖 3 應該可以幫助您更好地可視化系統響應。該圖顯示了 ADC 輸入電壓如何接近代碼轉換點。該圖顯示了具有不同初始值的兩種不同模擬的波形。在一項仿真中,ADC 輸入的初始值比目標代碼轉換點大 10 步(10ΔV)。在第二個中,初始值距代碼邊緣 10.001 步。

這里有一些值得一提的觀察結果。首先,ADC 輸入實際上并不等于轉換電壓。環路進入振蕩狀態,其中 ADC 輸入電壓是圍繞過渡電平振蕩的三角波(我們忽略 R 2 和 C 2 可能引入的濾波效應)。三角波形的平均值提供了代碼轉換點的估計。如圖 2 所示,可以使用具有內置平均運算功能的數字電壓表 (DVM) 來測量波形的平均值。

其次,圖 3 顯示在 ADC 輸入從轉換點落入一步之前存在瞬態響應。因此,平均過程應在信號穩定在最終平均值的可接受誤差范圍內后開始。

另外,應該注意的是,上述三角響應對應于無噪聲系統。在現實世界的系統中,不同組件引入的噪聲會導致一定程度的隨機性。這會將三角波形轉換為圍繞代碼邊緣值上下鋸齒狀的噪聲信號。圖 4 比較了噪聲 ADC 與無噪聲系統(類似于圖 3)的波形。

通常采用信號平均 技術來減少噪聲對測試結果的影響。決定反饋環動態的兩個主要因素是步長 (ΔV) 和系統中存在的噪聲水平。在本系列的下一篇文章中,我們將討論這兩個因素如何影響不同的參數。

ADC 內的采樣保持(S/H) 基本上由一個開關和一個采樣電容器組成。當開關在 ADC 采樣階段開始時閉合時,采樣電容器與前面的驅動電路共享其存儲的電荷。在圖 2 所示的示例中,內部采樣電容器與 C 2共享電荷。這會在采樣階段開始時在 ADC 輸入處產生干擾,稱為反沖噪聲。圖 5 說明了這種效果。

反沖效應會向 ADC 模擬輸入添加高頻、信號相關的毛刺。通過正確設計的系統,ADC 可以采集正確的樣本。然而,DVM 可能會在毛刺消失之前采集一些樣本,從而導致 ADC 輸入電壓平均值的測量不正確(參見圖 5)。

為了減少反沖噪聲,我們可以增加C 2電容的值 。然而,這需要降低采樣率(或等效地增加 ADC 采樣階段的持續時間)。因此,通過選擇C 2 為大電容,我們可以以更長的測量時間為代價來減少反沖效應。

圖 6 顯示了略有不同的伺服環路測試配置。在這種情況下,積分器輸入不是使用電流源,而是通過電阻器 (R) 連接到已知電壓(圖中的 +V 和 -V)。因此,輸送到積分器的電流為I=V/R。

值得一提的是,圖中提供的定性波形似乎不正確,因為在這種情況下三角波形具有衰減幅度,這與圖 3 和圖 4 中提供的典型波形不一致。

伺服環路測試的另一個版本如圖 7 所示。在這種情況下,模擬積分器被數字累加器取代,數字累加器根據比較器的輸出,在其先前值中添加或減去特定值 (N1)。

此外,DAC 用于將累加器輸出轉換為模擬值。生成轉換點估計值的模擬值被傳送到 ADC輸入,就像圖 2 中的圖表一樣。圖 3 中提供的仿真波形對應于圖 7 中的配置。

在本系列的下一篇文章中,我們將繼續討論,并了解如何根據所需的測量精度和系統中存在的噪聲來選擇此測試設置的不同參數。希望您現在了解了伺服環路 ADC 測試的基礎知識,甚至對 ADC 表征的困難有了一定程度的認識。