Marvell 推出業(yè)界首款 3nm SerDes和并行互連技術(shù)

2023-04-28 11:00:13 EETOP著眼于當(dāng)今繁重的數(shù)據(jù)基礎(chǔ)設(shè)施,Marvell已經(jīng)在臺積電的3納米工藝上實(shí)現(xiàn)了其SerDes和并行互連技術(shù)。

雖然半導(dǎo)體行業(yè)傳統(tǒng)上專注于晶體管,但互連現(xiàn)在也受到關(guān)注。促成這種興趣的因素有很多,包括更高的時鐘頻率、更小的節(jié)點(diǎn)大小以及小芯片等新技術(shù)。

上周, Marvell Technology 宣布首次在 3nm 節(jié)點(diǎn)上成功展示了其先進(jìn)的半導(dǎo)體互連技術(shù)。在本文中,我們將探討互連日益增長的重要性,以及 Marvell 最近發(fā)布的 SerDes 和并行互連技術(shù)在 TSMC 的 3nm 工藝上的應(yīng)用。

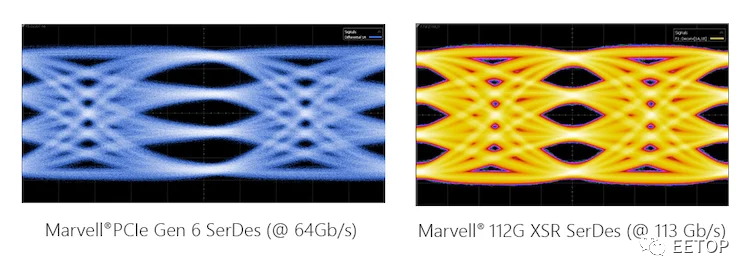

Marvell 的 3nm SerDes 眼圖。圖片由Marvell Technology提供

現(xiàn)代芯片互連

在當(dāng)今的半導(dǎo)體產(chǎn)業(yè)中,互連已經(jīng)成為芯片設(shè)計(jì)的一大瓶頸。

一個主要原因是現(xiàn)代芯片中互連寄生效應(yīng)越來越突出。減小晶體管節(jié)點(diǎn)尺寸導(dǎo)致器件到器件互連具有更小的幾何形狀和更大的電阻。出于同樣的原因,芯片的集成度越來越高,這意味著電感和電容耦合產(chǎn)生的寄生效應(yīng)正成為設(shè)計(jì)人員更加關(guān)注的問題。增加時鐘頻率等其他因素也有影響。

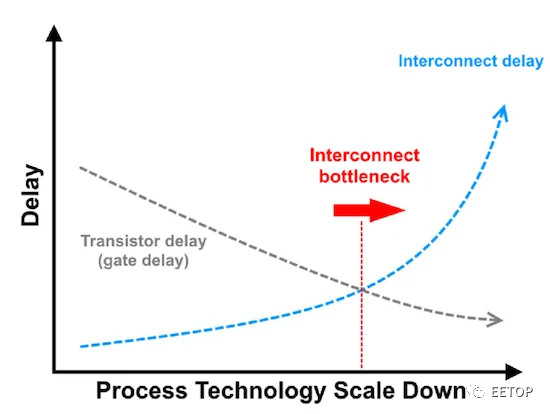

隨著工藝技術(shù)的縮小,互連延遲遠(yuǎn)遠(yuǎn)超過晶體管柵極延遲。

互連寄生效應(yīng)增加的結(jié)果是互連延遲成為比晶體管延遲更大的瓶頸,這意味著互連是芯片速度提升的最大障礙。同樣,互連寄生效應(yīng)已成為整體芯片功耗的主要貢獻(xiàn)者。

下一波計(jì)算浪潮中小芯片的激增進(jìn)一步加劇了這個問題的嚴(yán)重性,其中系統(tǒng)由通過高速互連連接的多個小芯片組成。為使半導(dǎo)體行業(yè)繼續(xù)發(fā)展并提供一代又一代更高的性能,開發(fā)人員必須創(chuàng)新當(dāng)前的互連設(shè)計(jì)。

Marvell 縮小 SerDes 和并行互連

Marvell 最近發(fā)布了一系列用于高級半導(dǎo)體互連的 SerDes 和并行互連解決方案。早在 2020 年,Marvell 就發(fā)布了業(yè)界首款用于數(shù)據(jù)中心的 112 G 5nm SerDes,這是該公司為未來計(jì)算基礎(chǔ)設(shè)施開發(fā)高性能芯片間互連所做努力的一部分。

上周,該公司宣布其在 3nm 節(jié)點(diǎn)上展示的互連技術(shù)。具體來說,Marvell在 TSMC 的 3nm 節(jié)點(diǎn)上實(shí)施了其 122 G XSR SerDes、Long Reach SerDes、PICe Gen 6 SerDes 和 240 Tbps 并行芯片到芯片互連。

據(jù) Marvell 稱,轉(zhuǎn)向 3nm 節(jié)點(diǎn)將幫助該公司為小芯片、定制 ASIC、以太網(wǎng)物理層設(shè)備等應(yīng)用解鎖更低功耗和更高性能的互連。

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章