433億晶體管,1020萬邏輯門,史上最大FPGA誕生!軟件工程師也可輕松駕馭!

2019-11-07 12:12:22 EETOP 原創11月6日,英特爾在北京舉辦的FPGA技術日活動中,發布了全球最大容量的全新FPGA:Stratix 10 GX 10M FPGA;同時宣布其革命性的開發工具-OneAPI,即將發布測試版,讓開發人員可同時駕馭CPU、FPGA、GPU、AI 四種不同芯片。

Stratix® 10 GX 10M FPGA是英特爾Stratix®10系列最新產品,產品正式發布之前,已有多家客戶收到樣片,目前該款FPGA已正式量產!

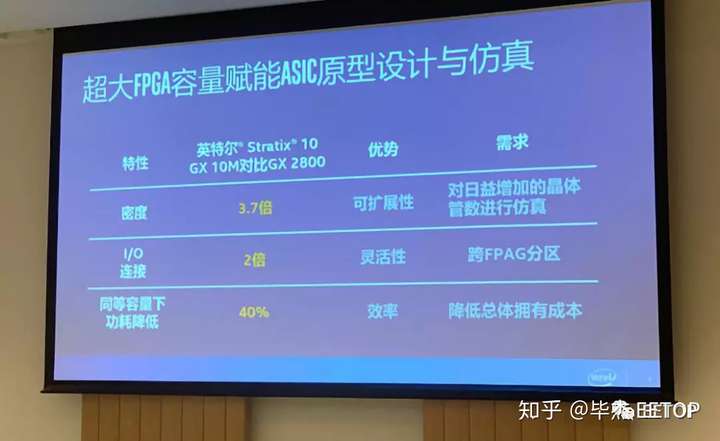

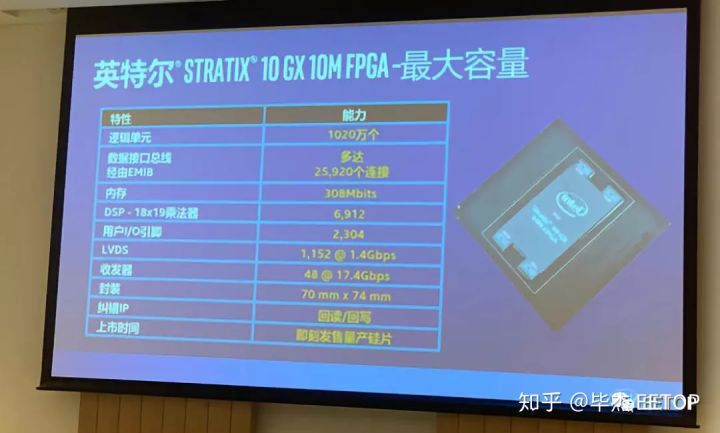

英特爾 Stratix 10 GX 10MFPGA 擁有1020 萬個邏輯單元,集成了433億個晶體管,其密度約為Stratix 10 GX 1SG280 FPGA 的 3.7 倍,后者為原英特爾 Stratix10 系列中元件密度最高的設備。

之所以可以做到如此之大,是因為其利用英特爾獨有的EMIB 封裝技術,融合了兩個高密度英特爾 Stratix 10 GX FPGA 核心邏輯晶片(每個晶片容量為 510 萬個邏輯單元)以及相應的 I/O 單元(PCIe4.0、UPI互連單元等)。

英特爾的 EMIB 技術只是多項 IC 工藝技術、制造和封裝創新中的一項,正是這些創新的存在,讓英特爾得以設計、制造并交付目前世界上密度最高(代表計算能力)的FPGA。

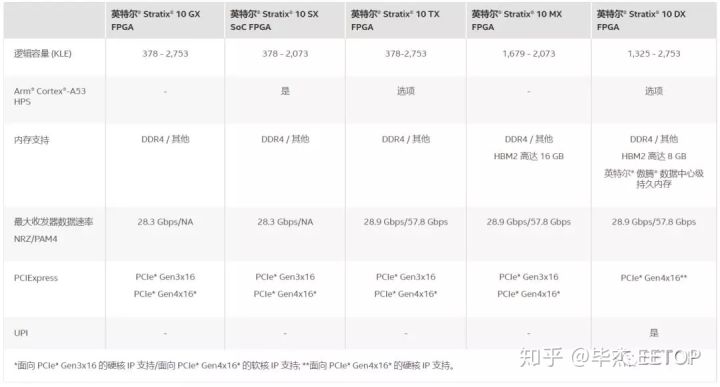

根據芯片內封裝的不同性能的功能小芯片,Stratix 10系列FPGA包括了SX、TX、MX、DX和GX不同型號。

GX FPGA沒有集成Arm Core,PCIe4支持軟IP,最大收發器速率28.3Gbps,可以看到相比更高性能的DX,GX定位于通用應用,主要被用于 ASICETTTT原型設計和仿真。

ASIC原型設計和仿真市場對當前最大容量的FPGA需求格外急切。有數家供應商提供商用現成(COTS) ASIC原型設計和仿真系統,對于這些供應商而言,能夠將當前最大的FPGA 用于ASIC 仿真和原型設計系統中,就意味著獲得了巨大的競爭優勢。此外,包括英特爾在內的很多大型半導體公司都開發了自定義原型設計和仿真系統,并在流片前使用該系統來驗證自身最大規模、最復雜、風險最高的ASSP 和SoC 設計。ASIC仿真和原型設計系統可以幫助設計團隊大幅降低設計風險。因此,包括英特爾 Stratix10 FPGA 和更早的Stratix® III、StratixIV 和Stratix V 設備在內的英特爾 FPGA,十多年來一直被用做很多仿真和原型設計系統的基礎設備。

ASIC 仿真和原型設計系統支持很多與IC 和系統開發相關的工作,包括:

仿真和原型設計系統旨在幫助半導體廠商在芯片制造前發現和避免代價高昂的軟硬件設計缺陷,從而節省數百萬美元。芯片在制造完成后修復硬件設計缺陷的成本要高得多,通常需要昂貴的重新設計費用。當設備制造出來并交付給終端客戶,解決這些問題的成本甚至會更高。正因為風險如此之高,且有可能節省的費用如此之多,這些原型設計和仿真系統為IC 設計團隊帶來了實實在在的價值。仿真和原型設計系統的使用已經越來越普及,因為在經濟風險如此之高的情況下,沒有哪個設計團隊負責人敢于忽視這項謹慎的驗證性投資。使用最大型的FPGA,就能夠在盡可能少的FPGA 設備中納入大型ASIC、ASSP和SoC 設計。英特爾 Stratix10 GX 10M FPGA是用于此類應用的一系列大型FPGA 系列中的最新設備。該款全新的英特爾 Stratix10 FPGA 支持仿真和原型設計系統的開發,適用于耗用億級ASIC 門的數字IC 設計。包含1020 萬個邏輯單元的英特爾 Stratix10 GX 10M FPGA,現已支持英特爾®Quartus® Prime 軟件套件。該套件采用新款專用IP,明確支持ASIC 仿真和原型設計。

英特爾 Stratix10 GX 10M FPGA 是第一款使用EMIB 技術并在邏輯和電氣上將兩個FPGA 構造晶片結合到一起的英特爾 FPGA,實現高達 1020 萬個邏輯單元密度。在該設備上,數萬個連接通過多顆EMIB 將兩個FPGA 構造晶片進行連接,從而在兩個單片FPGA 構造晶片之間形成高帶寬連接。以前,英特爾使用了 EMIB 技術將 I/O 和內存單元連接到 FPGA 構造晶片,從而實現了英特爾 Stratix10 FPGA 家族的規模和種類不斷擴張。例如,英特爾 Stratix10 MX 設備集成了8 GB 或16 GB的EMIB 相連的3D 堆疊HBM2 SRAM 單元。最近發布的英特爾 Stratix10 DX FPGA 則集成了EMIB 相連的P tile,具備PCIe 4.0 兼容能力。(英特爾首款支持硬核PCIe Gen4 及超路徑互連(UPI)FPGA量產出貨!)

英特爾 Stratix10 DX FPGA 中使用的P tile是兼容PCIe 4.0 的PCI-SIG 系統集成設備清單中的首款組件級設備。最近發布的英特爾®Agilex™ FPGA 中也同樣緊密集成了同款P tile,因而也能兼容PCIe 4.0 設備。英特爾 Stratix10 DX 和英特爾 AgilexFPGA 中使用的P tile是這一應用的又一絕佳范例,它展示了諸如EMIB的先進制造和生產技術,以及如何讓英特爾將一系列新產品快速推向市場,并投入全面生產。或許更重要的是,用來制造英特爾 Stratix10 GX 10M FPGA 的半導體和封裝技術,并不僅僅是為了制造世界上最大型的FPGA,這只是一個附加值,盡管相當重要,但并不是最重點。

在昨天的活動日上,英特爾邏輯事業部副總裁宣布oneAPI將于11月下旬發布測試版。

早在去年12月,英特爾就推出了“oneAPI”,顧名思義,“oneAPI”的目的就是提供統一的編程模型,簡化在不同硬件架構上的AI程序開發工作,讓開發者用一套源代碼創建適用于不同硬件的AI應用程序。

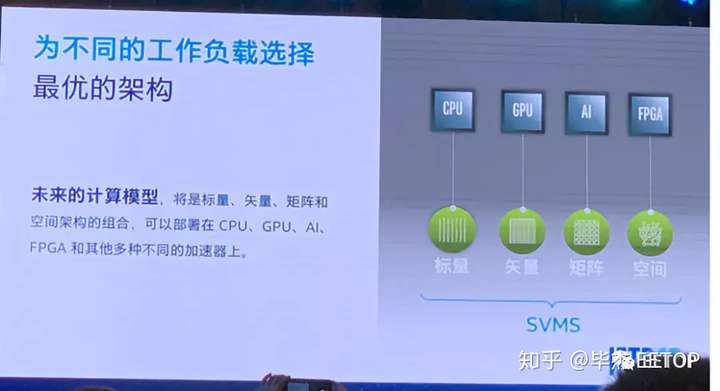

英特爾的產品覆蓋的廣泛計算架構包括標量(Scalar)、矢量(Vector)、矩陣(Matrix)和空間(Spatial),分別主要應用于CPU、GPU、AI加速器和FPGA產品。英特爾指出,在接下來五到十年中最重要的現代工作負載,就是這種標量、矢量、矩陣和空間架構的組合,英特爾稱之為SVMS架構。英特爾的oneAPI,便是從軟件層面來簡化和統一跨SVMS架構的創新。

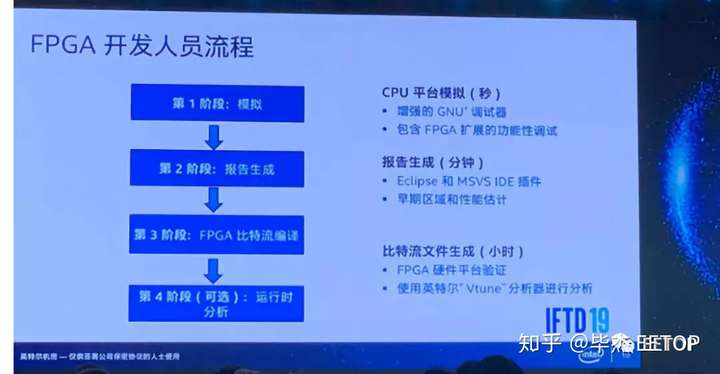

通過oneAPI,工程師將可以采用oneAPI所支持的并行C++語言,對這四種芯片進行編程,特別是對FPGA來說,現在軟件工程師也可以輕松完成設計了。

會后英特爾FPGA和電源產品營銷總裁Patrick Dorsey向EETOP記者解釋道:oneAPI開發FPGA主要是采用并行C++語言來實現算法庫的調用,這樣會大大加快FPGA的開發時間,但是性能相比直接用RTL語言開發的要弱一些,大約相當于70~80%。

關于oneAPI的更多補充

英特爾oneAPI概覽

英特爾oneAPI項目細節

直接編程語言Data Parallel C++

高性能庫推動人工智能和數據分析的發展