如果你是少數仍認為指令集架構(instruction set

architectures,ISA)是精簡(

RISC)或復雜(CISC),會對應用

處理器之設計的功耗或性能有顯著影響的軟體或硬體設計工程師,放棄

這種想法吧!它是不正確的,因為更重要的是

處理器的微架構(microarchitecture),也就是指令被硬布線(hardwired)到

處理器中

的方法,以及有什么被添加入以協助它們達成特定目標。

以上結論來自于學術期刊《ACM計算機系統學報(ACM Transactions on

Computer Systems)》的一篇論文“指令集架構之戰:了解ISA是CISC或

RISC的關聯性(ISA Wars:

Understanding the Relevance of ISA being CISC or

RISC)”(參考連結),作者為Emily

Blem、Jakrishnan Menon、Thiruvengadam Vijayaraghavan以及 Karthhikeyan

Sankaralingam;該論文報告了過去四年美國威斯康辛大學(University of Wisconsin)垂直研究小組(Vertical

Research Group,VRG)所做的一項研究結果。

報告作者之一Vijayaraghavan

表示,該研究是到目前為止針對三大

處理器架構──

英特爾(Intel) x86架構、

ARM處理器以及現屬于Imagination

的MIPS

處理器──的設計、實作等所有角度的最完整分析。“雖然在過去,

RISC與CISC指令集架構也許有一些差異,但我們鎖定的參數──性能

(performance)、功耗(power)與能源效益(energy)現在肯定沒有。”另一位報告作者Sankaralingam

表示:“ISA缺乏的地方,微架構就會補強它,反之亦然。”

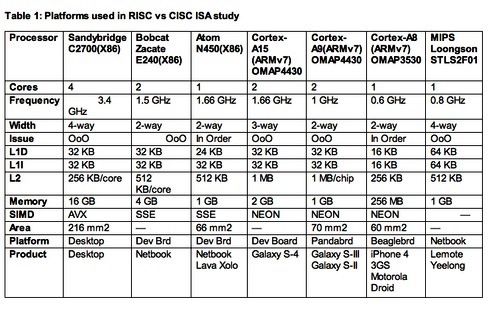

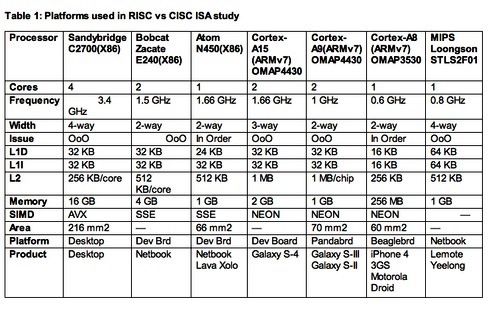

RISC

RISC、CISC指令集架構研究所采用的

處理器平臺

Sankaralingam

指出,現在只有一種

處理器是真正的

RISC架構──MIPS,是以美國史丹佛大學開發的

RISC架構為基礎;至于x86

處理器架構一開始是純CISC設

計,但過去幾年來越來越朝類

RISC結構發展。

ARM處理器架構近似

RISC,但采用更多CISC功能,包括增加的Thumb 1與Thumb

2指令集架構。

他表示:“所以我們的研究基本上是在目前的市場環境,比較今日的Intel、

ARM與MIPS

處理器;幾乎每一個我們的量

測結果,都與指令集架構無關。”以往的比較研究會因為

處理器系統的軟體與硬體資源不同而有缺陷,但VRG團隊盡力確保其量測是在條件幾乎相同的平臺與同等

的環境中完成,為了區分出實作與ISA效果,他們盡可能讓所使用的各種ISA晶片,都具備類似的微架構。

此研究將比較樣本局限在

ARM

Cortex-A8或更高等級的

處理器,較不注重Cortex-M系列元件;Sankaralingam解釋:“原因很簡單,我們的目標之一是要有能比較

與量化的平臺,因此我們沒必要去看A9以下的

處理器,以及相對應的競爭架構。”在Cortex-M0的環境下,

ARM是與1~20MHz與

2~50mWatt的8位元MCU競爭,其運作是架高在x86指令集之上,不適用其研究。

該研究小組的評估,是以一顆MIP

處理器(中國

開發的龍芯- Loongson

處理器)、三個

ARM平臺(Cortex-

A8、Cortex-A9與Cortex-A15),以及三個x86架構設計(Atom、Bobcat與Sandybridge

i7)來進行;他們也使用了相同的作業系統──Linux 2.6 LTS,還有以gss 4.4為基礎的交叉編譯器前端(cross compiler

front end)。

在行動裝置客戶端的工作負載方面,他們使用CoreMark與Webkit性能基準;在桌上型應用方面,則是采用SPEC

CPU2006基準。至于伺服器工作負載的性能基準,則是使用包括lightpd與CLucerne等性能基準。

RISC

RISC、CISC指令集架構研究的發現

研究所采用的實作樣本,包括不同ISA以及相同ISA、不同微架構;Sankaralingam表示:“整體看來,我們選擇的平臺條件具備合理的平等,而且我們執行了詳細的分析,分別得出各微架構與技術的效果。”

VRG

團隊確實進行了

處理器在執行時間(execution time)、工作周期(cycle count)、指令數目(instruction

count)、指令格式與結構(instruction format and

mix)、微架構以及ISA對微架構影響的比較;功耗與能源效益的分析量測也很全面,包括平均功耗、平均技術獨立功耗(technology

independent power),以及平均能源效益等等。

Sankaralingam表示,他們的報告結論是,雖然ISA與支援不

同特殊應用(例如虛擬化、加速器、浮點運算..)的功耗與性能有關,但無論ISA是

RISC或CISC,其實大都與今日成熟的微

處理器設計領域沒有什么關

系。“根據這項研究,開發工程師能簡單根據工程設計觀點,放心考慮針對不同性能等級最佳化的

ARM、MIPS或x86處理

器;”Sankaralingam指出:“不同ISA的能源效益基本上并沒有差別。”

如該報告最后一段所寫:“顯然數十年來的硬體與編譯器研發,已經能有效掌握

RISC與CISC架構,而且兩者在未來訴求節能的創新應用中擁有平等地位。”