全球頂尖芯片專家揭秘【低功耗芯片設(shè)計(jì)】真相

2019-01-08 12:39:52 清谷資本作者:新帆人(清谷資本)

摘要

低功耗芯片設(shè)計(jì)是本世紀(jì)以來最重要的新興設(shè)計(jì)方法。可以說沒有低功耗設(shè)計(jì),就沒有今天的智能手機(jī),移動(dòng)設(shè)備,物聯(lián)網(wǎng),及高性能計(jì)算等產(chǎn)業(yè)。本文從芯片功耗和電源噪聲的分析開始,介紹了低功耗設(shè)計(jì)的幾種常用方法,并給出了低功耗設(shè)計(jì)的幾種可能的發(fā)展方向。可以預(yù)見,作為一種最新的芯片設(shè)計(jì)方法,隨著芯片圖形尺寸越來越小,低功耗設(shè)計(jì)在現(xiàn)在及未來的芯片中會(huì)起到越來越重要的作用。

——新帆人

回顧芯片設(shè)計(jì)的發(fā)展,我們看到大致可以分為三個(gè)階段:

第一個(gè)為解決設(shè)計(jì)復(fù)雜度的階段:80年代開發(fā)的邏輯綜合工具極大得提高了設(shè)計(jì)效率及規(guī)模;第二個(gè)為提高時(shí)鐘頻率的階段:90年代為了提高運(yùn)算速度,時(shí)鐘頻率從幾十MHz提高到幾百M(fèi)Hz,甚至達(dá)到了GHz。(例如本世紀(jì)初Digital公司的Alpha芯片的時(shí)鐘頻率為1.4GHz)。芯片設(shè)計(jì)也是圍繞著時(shí)鐘頻率與時(shí)序進(jìn)行,例如像時(shí)序驅(qū)動(dòng)的邏輯綜合及布局布線等。第三個(gè)為低功耗設(shè)計(jì)階段。我們知道,CMOS電路(絕大多數(shù)集成電路芯片都采用CMOS電路)的動(dòng)態(tài)功耗(也叫工作功耗)與時(shí)鐘頻率成正比,同時(shí)也與電源電壓的平方成正比。這樣一來,隨著時(shí)鐘頻率的增加,芯片的功耗也隨之快速上升(例如Alpha芯片的功耗為125瓦)。進(jìn)入二十一世紀(jì)后,人們逐漸認(rèn)識到單純靠增加時(shí)鐘頻率再也不能提高性能了。相反的,功耗的增加帶來了一系列問題。例如芯片溫度增高引起的散熱及電路性能下降,電源及信號噪聲管理(power integrity - PI, signal integrity - SI)等。本世紀(jì)初以來移動(dòng)設(shè)備特別是手機(jī)的興起更是引發(fā)了低功耗芯片設(shè)計(jì)的浪潮。

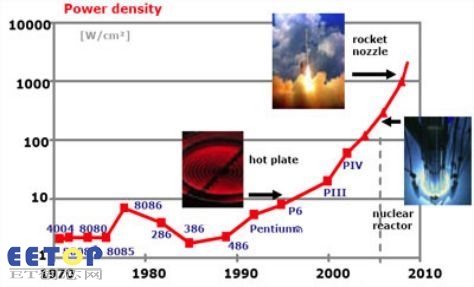

英特爾曾在1999年給出了其處理器功率密度隨著時(shí)間的變化(如圖1所示)。可以看到,按照當(dāng)時(shí)的發(fā)展趨勢(摩爾定律),晶體管的尺寸逐年縮小,芯片上的功率密度將很快達(dá)到甚至超過核反應(yīng)堆甚至火箭噴口的功率密度 --- 這是一個(gè)不可控的狀態(tài)。因此,當(dāng)時(shí)的業(yè)界共識是35納米就是工藝水平及其電路的極限了。

圖1:英特爾處理器功率密度的發(fā)展趨勢(1999的預(yù)測數(shù)據(jù))

然而事實(shí)上,現(xiàn)在的工藝水平已經(jīng)達(dá)到了7納米,而且還在繼續(xù)往前發(fā)展。這里面低功耗設(shè)計(jì)功不可沒。可以說沒有低功耗設(shè)計(jì),就沒有納米級的電路及芯片,更不用說我們?nèi)巳耸褂玫闹悄苁謾C(jī)了。

下面我們簡單介紹一下芯片上的電源網(wǎng)絡(luò)以及低功耗設(shè)計(jì)常用的方法。

我們知道,芯片功耗主要由三部分組成:動(dòng)態(tài)功耗(也叫開關(guān)功耗),短路功耗,及靜態(tài)功耗(也叫泄漏功耗)。其中動(dòng)態(tài)功耗是邏輯門在工作時(shí)給負(fù)載電容充放電引起的,短路功耗是邏輯電路翻轉(zhuǎn)過程中造成瞬態(tài)短路引起的,而靜態(tài)功耗是由于邏輯電路中的泄漏電流引起的。因此,低功耗設(shè)計(jì)主要是圍繞著如何減少這三部分功耗來進(jìn)行的。

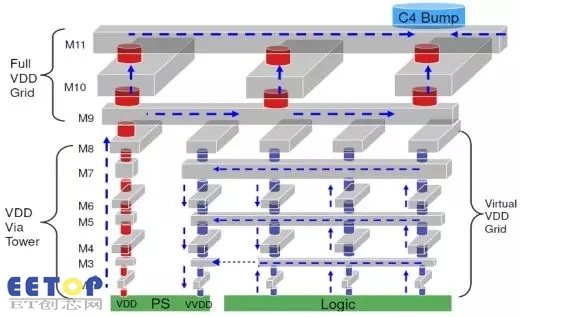

平時(shí)我們看到的電路圖里面的電源線(及地線)都是一根細(xì)細(xì)的導(dǎo)線。實(shí)際上,芯片里面的電源網(wǎng)絡(luò)十分復(fù)雜。圖2給出了一個(gè)典型的芯片電源網(wǎng)絡(luò)。可以看到,從最上面的封裝接觸點(diǎn)(C4)到最下面的晶體管電路(Logic),導(dǎo)線多達(dá)十幾到幾十層。每兩層導(dǎo)線中間有通孔(Via)連接。從上至下,導(dǎo)線由寬到窄,由厚到薄。這些導(dǎo)線形成一個(gè)龐大的由寄生電阻電容組成的網(wǎng)絡(luò)(如果工作頻率很高,還要加上寄生電感)。如今的一個(gè)系統(tǒng)集成(SoC)芯片里,電源網(wǎng)絡(luò)里的節(jié)點(diǎn)數(shù)以及寄生器件可達(dá)數(shù)十億之多。

我們可以把芯片上的電源網(wǎng)絡(luò)比喻成一個(gè)龐大的輸水灌溉系統(tǒng):電源就是水庫,電源導(dǎo)線就是水渠,而晶體管則是地里的莊稼。水渠起到的作用就是把水從水庫輸送到田里的莊稼。引水的水渠也是由寬到窄,由深到淺,最終將水引導(dǎo)并澆灌到每一顆莊稼上。

電源噪聲及其影響

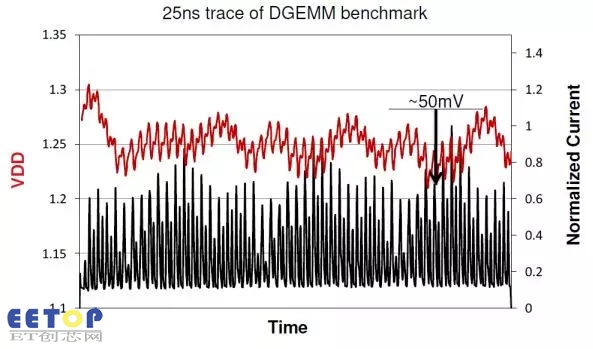

最初人們在設(shè)計(jì)電路時(shí),總是假定電源電壓是個(gè)恒定值。實(shí)際上,電源網(wǎng)絡(luò)上的電壓并不是恒定的設(shè)計(jì)值,而是隨著電路的工作上下起伏。這是因?yàn)?a href="http://www.xebio.com.cn/analog_power" target="_blank" class="keylink">電源網(wǎng)絡(luò)上有很多的寄生電阻和電容(如果工作頻率足夠高的話還要考慮寄生電感)。如果電源網(wǎng)絡(luò)設(shè)計(jì)得不好,就會(huì)造成電壓起伏過大,從而導(dǎo)致電路性能下降,甚至不工作。圖3給出了芯片電源上的電源電壓及電流。可以看到,在短短的幾納秒內(nèi),電源電壓的變化就達(dá)到50毫伏。

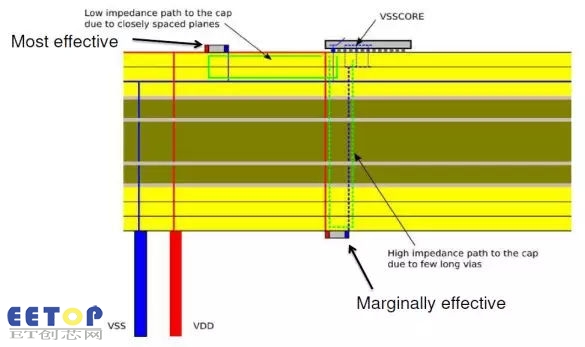

一種有效減少電源電壓噪聲的方法是在電源網(wǎng)絡(luò)上加去耦合電容(decoupling capacitor)。去耦合電容就像安放在水渠旁防旱澇的蓄水池:當(dāng)水位過高時(shí),可以往蓄水池里放水以防止水位高過河床。當(dāng)水位過低時(shí),可以把蓄水池里的水放到水渠里,以保證水渠里的水位穩(wěn)定。同樣的,去耦合電容也起到穩(wěn)定電源電壓的作用。去耦合電容可以分成幾類:芯片級,它們的電容值最小,在fF(1E-15F)范圍;封裝級,它們的電容值居中,在pF范圍(1E-12F);以及電路板級,它們的電容值最大,在nF-uF范圍(1E-9F到1E-6F)。可以看到,它們的電容量有數(shù)量級的差別,分別用來過濾不同頻段的噪聲(100MHz-1GHz, 10MHz-100MHz, 100KHz-10MHz)。值得注意的是芯片上的元器件也會(huì)對去耦合電容有所貢獻(xiàn)(例如晶體管上的寄生電容,以及導(dǎo)線之間的耦合電容)。如何擺放去耦合電容是個(gè)十分復(fù)雜的問題。如果去耦合電容離工作單元擺得過遠(yuǎn),則起不到減少電壓噪聲的作用。就像蓄水池如果離水渠過遠(yuǎn),就無法及時(shí)調(diào)節(jié)水位。圖4給出了電路板上的兩個(gè)去耦合電容的例子。可以看到,由于上面的去耦合電容離芯片近,其所起的作用就遠(yuǎn)遠(yuǎn)好過下面的去耦合電容。

圖4:電路板(PCB)上的去耦合電容

為了保證電源電壓噪聲不影響電路的正常工作,就需要對整個(gè)芯片進(jìn)行電壓噪聲分析。電壓噪聲分析可以幫助設(shè)計(jì)者發(fā)現(xiàn)電源網(wǎng)絡(luò)中的薄弱環(huán)節(jié),以及芯片上的“熱點(diǎn)”(hot-spot),即芯片上功耗和電源噪聲最大的地方,以便加以改進(jìn)。電壓噪聲分析的方法分為靜態(tài)和動(dòng)態(tài)兩種。靜態(tài)方法是在上個(gè)世紀(jì)90年代后期開發(fā)的。它的基本思想很簡單,就是把電源網(wǎng)絡(luò)看成一個(gè)龐大的電阻網(wǎng)絡(luò),把電路里的每個(gè)邏輯門看成一個(gè)直流電流源,然后來解歐姆定律:(1/R)V=I。注意這是在求解全芯片的歐姆定律,網(wǎng)絡(luò)里包含從數(shù)百萬到數(shù)十億個(gè)電阻,以及數(shù)百萬到數(shù)億個(gè)電流源,非常具有挑戰(zhàn)性。然而把芯片工作狀態(tài)當(dāng)成直流的歐姆定律來解也有很多局限。最明顯的就是CMOS是動(dòng)態(tài)工作的電路,把一個(gè)真實(shí)的瞬態(tài)電流及電壓波形用一個(gè)固定的直流值來代替,會(huì)損失很多精度。

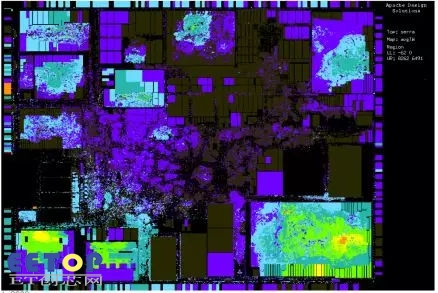

到了本世紀(jì)初,人們意識到以上靜態(tài)分析方法的局限,因此開發(fā)了用真實(shí)的瞬態(tài)電流波形來做動(dòng)態(tài)模型與分析。這個(gè)難度比靜態(tài)分析還要大一個(gè)數(shù)量級。首先電源網(wǎng)絡(luò)上除了寄生電阻之外,還要考慮寄生電容以及去耦合電容。如果工作頻率很高,或者分析中包含芯片封裝的話,還要考慮寄生電感效應(yīng)。其次要進(jìn)行時(shí)域的瞬態(tài)分析。因此在高性能的服務(wù)器上跑一個(gè)瞬態(tài)分析下來要用2-3天的時(shí)間。動(dòng)態(tài)分析的優(yōu)點(diǎn)是它的高精確度,它的結(jié)果更接近真實(shí)物理狀況(例如可以看到去耦合電容效應(yīng)),是芯片設(shè)計(jì)里不可或缺的分析工具(sign-off analysis tool)。圖5給出了一個(gè)全芯片的動(dòng)態(tài)壓降分布圖。

圖5:全芯片的動(dòng)態(tài)壓降圖

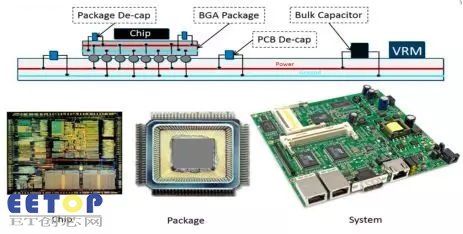

在以往的設(shè)計(jì)過程中,芯片,封裝,和系統(tǒng)都是分開進(jìn)行的。自從有了以上的功耗分析工具后,設(shè)計(jì)者就可以進(jìn)行整體的分析及優(yōu)化。例如,以前封裝的設(shè)計(jì)者沒有芯片精確的功耗模型,只好要么用粗略的估算,要么留出過多的余量。而現(xiàn)在有了芯片功耗分析工具之后,就可以產(chǎn)生精確的芯片功耗模型(Chip Power Model – CPM),使得芯片-封裝-系統(tǒng)的整體優(yōu)化成為可能。圖6給出了芯片-封裝-系統(tǒng)的整體優(yōu)化的示意圖。

低功耗電路設(shè)計(jì)方法

上面講到了功耗以及它帶來的電源噪聲。為了減少功耗及其影響,過去十多年來發(fā)展了很多低功耗設(shè)計(jì)方法。例如,既然動(dòng)態(tài)功耗與電壓的平方成正比,我們可以對芯片內(nèi)部的電路使用低電壓(比如1.0V),而芯片上對外接口的驅(qū)動(dòng)電路使用高電壓(比如3.3V),這就是所謂的多域電源設(shè)計(jì) (Multi-power domain)。對芯片內(nèi)部的電路還可以再細(xì)分,比如對需要高速運(yùn)算的電路(像時(shí)鐘驅(qū)動(dòng)電路)采用低閾值的邏輯單元,雖然它的泄漏電流要大一些,但可以滿足短延遲的要求。對一般的邏輯電路可以采用高閾值的邏輯單元以減少泄漏電流。這就是所謂的多閾值邏輯單元設(shè)計(jì) (Multi-Vt CMOS)。時(shí)鐘電路的動(dòng)態(tài)功耗通常要占到芯片總體動(dòng)態(tài)功耗的30-40%甚至更多,因此芯片設(shè)計(jì)者們也把時(shí)鐘分成了許多域(Multi-clock domain),有的芯片上時(shí)鐘域甚至達(dá)到了數(shù)百個(gè)之多。

下面我們就來介紹幾個(gè)典型的低功耗設(shè)計(jì)與管理方法。

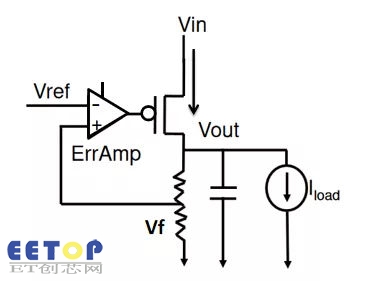

低壓降穩(wěn)壓器(Low Drop-Out regulator - LDO)

低壓降穩(wěn)壓器是一種直流線性穩(wěn)壓器,其電路由PMOS傳輸門,高增益誤差放大器,及分壓電阻組成(有時(shí)也帶有去耦合電容)。它可以提供大范圍的電源電壓輸出,具有噪聲小,低成本,集成度高的優(yōu)點(diǎn),因此在低功耗設(shè)計(jì)中廣泛使用。

圖7:低壓降線性穩(wěn)壓器

低壓降穩(wěn)壓器的工作原理是利用反饋來進(jìn)行穩(wěn)壓的。從圖7可以看到,PMOS傳輸門的輸出端(漏極),亦即LDO的輸出端通過分壓電阻接到了增益放大器的輸入端,而增益放大器的輸出端又接到了PMOS傳輸門的輸入端(柵極)。因此,LDO輸出的電流和電壓將會(huì)受到傳輸門的控制。其反饋工作原理如下:Iload 增大,Vout 下降,導(dǎo)致Vf 下降,Vin=Vf – Vref 下降,PMOS的柵壓Vgate 下降,Vgs = Vin – Vgate 增大,Ipmos( Iload )增大,Vout下降減小,因而達(dá)到穩(wěn)壓的目的。

當(dāng)然,真正芯片上的LDO電路會(huì)比上面的原理圖復(fù)雜很多。例如采用多級的誤差放大器,PMOS傳輸門陣列等等。但基本原理是一樣的。

動(dòng)態(tài)壓頻調(diào)節(jié)

(Dynamic Voltage Frequency Scaling - DVFS)

動(dòng)態(tài)壓頻調(diào)節(jié)主要針對的是減少動(dòng)態(tài)功耗。我們知道,動(dòng)態(tài)功耗和電路工作頻率成正比,也和電源電壓的平方成正比。因此,如果能隨時(shí)判斷出電路的工作狀態(tài),并隨之調(diào)整工作頻率及電源,就可以達(dá)到減少功耗的目的。

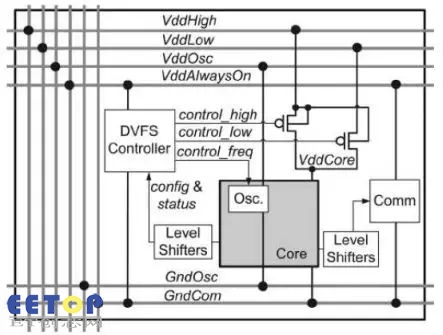

圖8:具有兩個(gè)電壓值(VddHigh, VDDLow)的動(dòng)態(tài)壓頻調(diào)節(jié)原理圖

圖8給出了一種動(dòng)態(tài)壓頻調(diào)節(jié)的實(shí)現(xiàn)原理圖。首先,提供了兩個(gè)電源電壓VDDHigh和VDDLow,電壓控制的震蕩器(VCO),以及動(dòng)態(tài)壓頻調(diào)節(jié)控制器(DVFS Controller)。

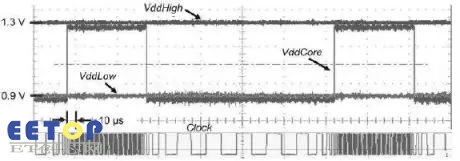

動(dòng)態(tài)壓頻調(diào)節(jié)控制器會(huì)根據(jù)電路的工作狀態(tài)來決定電源電壓和工作頻率。例如,當(dāng)執(zhí)行一個(gè)訪問存儲器的指令時(shí),需要好幾個(gè)時(shí)鐘周期,這時(shí)就可以降低運(yùn)算邏輯電路的電源電壓及工作頻率,等下一組數(shù)據(jù)傳回來后,再把運(yùn)算邏輯電路的電源電壓及工作頻率恢復(fù)回來,以便滿足性能的要求。圖9給出了處理器內(nèi)核的電源電壓(VddCore)隨著工作狀態(tài)在兩個(gè)電源電壓(VddHigh=1.3V, VddLow=0.9V)之間變化的波形。同時(shí)還給出了時(shí)鐘變化的波形。可以看到,當(dāng)電源電壓為VddLow時(shí),時(shí)鐘頻率也隨之降低了。

圖9:具有兩個(gè)電壓值(VddHigh, VDDLow)的動(dòng)態(tài)壓頻調(diào)節(jié)波形圖

動(dòng)態(tài)壓頻調(diào)節(jié)是為了減少芯片工作時(shí)的功耗,因此設(shè)計(jì)者需要十分了解芯片上各個(gè)模塊的工作狀態(tài),才能設(shè)計(jì)出好的動(dòng)態(tài)壓頻調(diào)節(jié)控制器,同時(shí)在時(shí)序優(yōu)化上也要考慮到電壓的變化。一個(gè)好的動(dòng)態(tài)壓頻調(diào)節(jié)可以做到節(jié)省20%的動(dòng)態(tài)功耗。

電源閥門(Power Gating)

電源閥門主要針對的是靜態(tài)功耗(泄漏電流引起的功耗)。其基本思想就是在某些功能模塊不工作時(shí),把它的電源斷開。這是因?yàn)樵诰w管的亞閾值范圍內(nèi),泄漏電流與電壓是呈指數(shù)的關(guān)系,因此這種方法對減小靜態(tài)功耗效果十分顯著。圖10給出了電源閥門的示意圖。其中的開關(guān)是用MOSFET晶體管做的。這個(gè)開關(guān)把電源分成了兩個(gè)區(qū)域:連接電源的一邊叫真實(shí)電源域(VDD domain),連接電路的一邊叫虛擬電源域(Virtual VDD domain)。真實(shí)電源域的電壓值是不變的,而虛擬電源域的電壓值是根據(jù)電源閥門的狀態(tài)改變的。當(dāng)電源閥門閉合時(shí)(ON),虛擬電源域的電壓值十分接近VDD(VDD減去電源閥門上的壓降);而當(dāng)電源閥門斷開時(shí) (OFF),虛擬電源域的電壓值十分接近0(電源閥門的漏電流與電路靜態(tài)電阻的乘積)。

除了把電源閥門放在VDD上,也可以把電源閥門放在VSS上。其相對應(yīng)的叫虛擬VSS域(Virtual VSS domain)。VDD上的電源閥門叫頭開關(guān)(header switch),而VSS上的電源閥門叫腳開關(guān)(footer switch)。

圖10:電源閥門示意圖

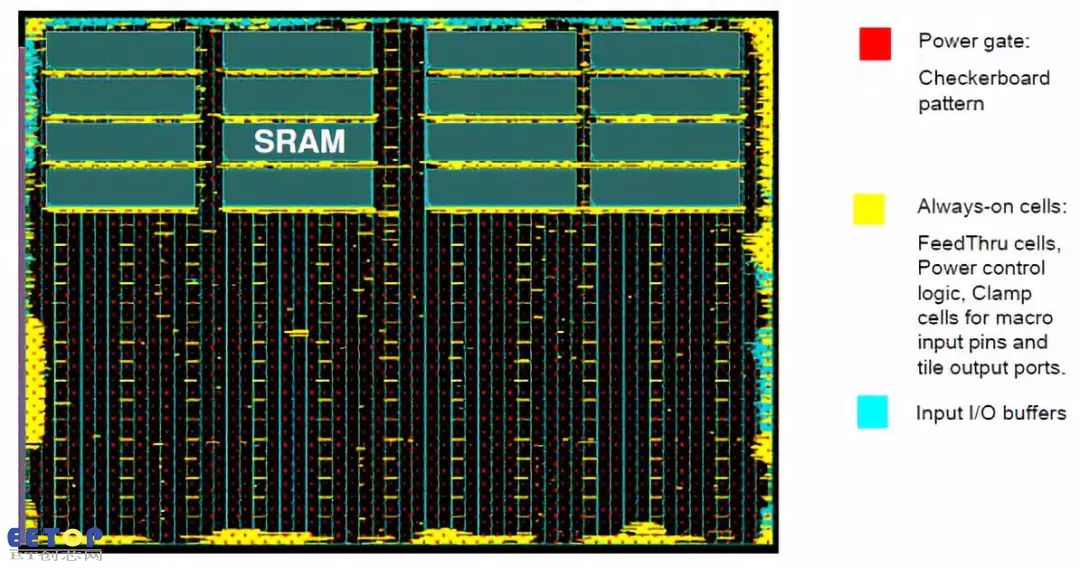

從上面我們可以看到,要實(shí)現(xiàn)一個(gè)理想的電源閥門,會(huì)對這個(gè)小小的開關(guān)有很多要求:導(dǎo)通時(shí)的電阻值要小;斷開時(shí)電阻值要很大(以減小其漏電流);開啟和斷開的響應(yīng)要快。實(shí)際上,芯片里的電源閥門不只是單獨(dú)一個(gè)晶體管開關(guān),而是由成百上千個(gè)晶體管開關(guān)組成的。如何擺放這成百上千個(gè)電源閥門,需要進(jìn)行準(zhǔn)確的計(jì)算和分析。圖11給出了一個(gè)電源閥門在芯片上的布局。每一個(gè)紅點(diǎn)代表一個(gè)電源閥門開關(guān)。可以看到,很多電源閥門分布在各個(gè)功能模塊的電路周圍,在靜態(tài)存儲器周圍也布有電源閥門。

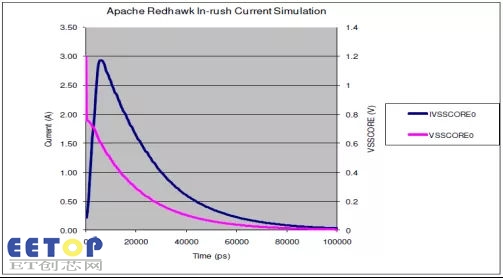

在設(shè)計(jì)電源閥門時(shí),一個(gè)很重要的步驟就是分析其開啟過程。電源閥門的開啟過程就像水庫開閘放水一樣。一方面希望盡量在短時(shí)間內(nèi)完成,但另一方面又要可控,使得涌流不能太大(in rush current)。如果涌流太大,就會(huì)影響到旁邊的電路模塊的電壓穩(wěn)定,也會(huì)產(chǎn)生電源線/地線上的噪聲。長期多次的大涌流會(huì)造成電子飄移 (EM – Electron Migration),使得導(dǎo)線斷開或短路,就像水庫開閘放水,如果水流過大,就有可能沖開河堤一樣。因此,這些電源閥門并不是同時(shí)開啟的,而是按照一定的順序和時(shí)間依次打開的。這樣就可以有效地控制涌流。

圖12給出了一個(gè)使用腳開關(guān)的開啟分析結(jié)果。可以看到,在100ns期間,VSS(粉色曲線)從3V降到0V,而電流(藍(lán)色曲線)在10ns時(shí)達(dá)到了近3A的峰值。

圖12:電源閥門(腳開關(guān))開啟時(shí)的電壓VSS與電流I(VSS)隨時(shí)間的變化

結(jié)語

如我們之前所說,功耗已經(jīng)成為目前芯片設(shè)計(jì)中最重要的因素。

1)功耗會(huì)影響電路性能,芯片散熱,以及芯片可靠性等一系列問題;

2)芯片的功能及時(shí)序設(shè)計(jì)與優(yōu)化已相對成熟,但功耗上的優(yōu)化還有很多文章可做;

3)電源電池容量的增加相對有限,而且受到安全因素的限制(例如前些時(shí)候發(fā)生的三星手機(jī)電池爆炸)。

以上我們介紹了在電路級上進(jìn)行低功耗設(shè)計(jì)及優(yōu)化。實(shí)際上,人們也在探索在其它設(shè)計(jì)層次上的低功耗設(shè)計(jì)及優(yōu)化。例如,現(xiàn)在已經(jīng)開發(fā)出了寄存器傳輸級(RTL)上的功耗估算及優(yōu)化。架構(gòu)級( architecture)上的功耗估算及優(yōu)化也在研發(fā)中。這是由于越早在設(shè)計(jì)周期中及越高層次的設(shè)計(jì)中考慮功耗,就會(huì)得到越大的回報(bào)。除了在硬件上進(jìn)行功耗優(yōu)化,人們也在從軟件角度來進(jìn)行降低功耗的努力。最明顯的例子就是操作系統(tǒng)級里的電源管理,把不在運(yùn)行的程序和App放置在休眠狀態(tài)(sleep mode)。除此之外,人們也在探索在編譯器里加入功耗優(yōu)化的功能,使得程序和App在運(yùn)行中也可以達(dá)到功耗最低。可以預(yù)見,隨著器件工藝,電路設(shè)計(jì),系統(tǒng)集成,和軟件開發(fā)的不斷完善,低功耗設(shè)計(jì)也會(huì)在以上的各個(gè)方面不斷發(fā)展進(jìn)步。

EETOP 官方微信

創(chuàng)芯大講堂 在線教育

半導(dǎo)體創(chuàng)芯網(wǎng) 快訊

相關(guān)文章