上海微系統所在三維存儲器設計領域取得重要進展

2017-09-16 22:47:57 n近日,中國科學院上海微系統與信息技術研究所相變存儲器課題組在三維存儲器設計領域取得重要進展,相關成果以"A Single-Reference Parasitic-Matching Sensing Circuit for 3-D Cross Point PCM"為題,發表在國際集成電路重要期刊(前六位)IEEE Transactions on Circuits and Systems II: Express Briefs [vol. PP, no. 99, 2017]上。這是世界上首篇關于三維相變存儲器讀出電路設計的文章,也是SCI刊物三維相變存儲器電路設計發表的首篇文章。

相變存儲器利用電脈沖誘導存儲材料在非晶態與晶態之間切換,具有非揮發性、循環壽命長、寫入速度快、穩定性好、功耗低等優點,被業界認為是下一代存儲技術的最佳解決方案之一。

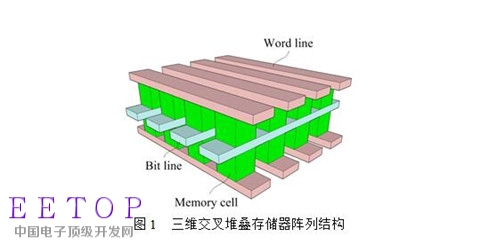

三維集成技術通過芯片或器件在垂直方向的堆疊,可以顯著增加芯片集成度,是延續摩爾定律的一種重要技術。其中,一種交叉堆疊(cross point)的三維存儲結構被廣泛應用于非易失存儲器。

當前,三維新型非易失存儲器的研究主要集中在器件和陣列層面。與傳統的二維存儲器不同,三維相變存儲器采用了新型的雙向閾值開關(Ovonic Threshold Switch,OTS)器件作為選通器件(selector)。根據OTS器件的物理特性和三維交叉堆疊陣列結構的特點,三維交叉堆疊型相變存儲器采用一種V/2偏置方法以實現存儲單元的操作。但V/2偏置方法和OTS器件導致陣列中諸多未被選擇的存儲單元的漏電。漏電導致讀出電路讀取正確率和讀出速度的下降。存儲器在進行讀操作時,陣列中的寄生器件會降低讀取速度。二維存儲器中,這些器件主要集中在平面方向;但在三維存儲器中,垂直方向的寄生器件會進一步降低讀取速度。因此,對于影響三維存儲器讀操作各因素的量化分析和提高其速度的集成電路設計是必要的。

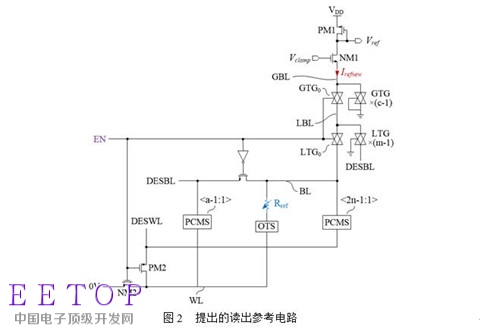

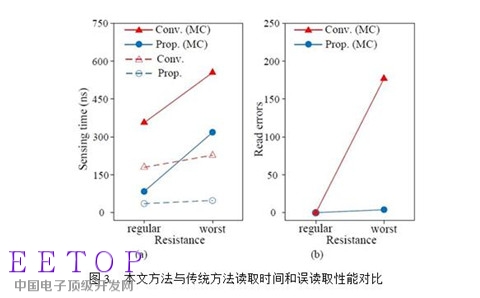

三維相變存儲器的具體工程細節屬商業機密,可參考資料較少。中國科學院上海微系統與信息技術研究所雷宇等人首先設計了三維相變存儲器的陣列核心電路,再對三維相變存儲器的讀路徑進行了分析,最終總結了影響三維相變存儲器讀操作的五種因素。這五種因素與三維存儲器陣列參數的量化關系也被指出。以此為基礎,論文提出了一種適用于三維存儲器的單參考和寄生匹配讀出電路。該電路采用變化參考電流,并對以上五種因素在讀方向和參考方向進行了匹配。實驗結果表明,讀出時間比傳統方法縮短了79%,誤讀取個數下降了97%。

論文提出的讀出電路還可適用于其它三維交叉堆疊型非易失存儲器。并因讀出電路與陣列的設計參數直接相關,相關設計人員可根據其存儲器的容量,方便的設計出適用于不同容量存儲器的、高性能的讀出電路。

該論文在國際上首次歸納分析了對三維交叉堆疊型存儲器讀操作有影響的五種因素,提出了第一種與三維新型非易失存儲器陣列特性相關的讀出電路,也是世界上首篇關于三維相變存儲器讀出設計的文章。

中國科學院上海微系統與信息技術研究所信息功能材料國家重點實驗室是論文的第一單位,中國科學院大學是論文的第二單位。上海微系統所博士生雷宇為論文的第一作者,陳后鵬研究員為論文通訊作者,研究工作在宋志棠研究員的領導下展開。論文于2016年12月投出。該研究工作得到了中國科學院戰略性先導科技專項、國家集成電路重大專項、國家自然科學基金、上海市科委等支持。

論文鏈接:http://ieeexplore.ieee.org/document/7987059/ DOI: 10.1109/TCSII.2017.2729665