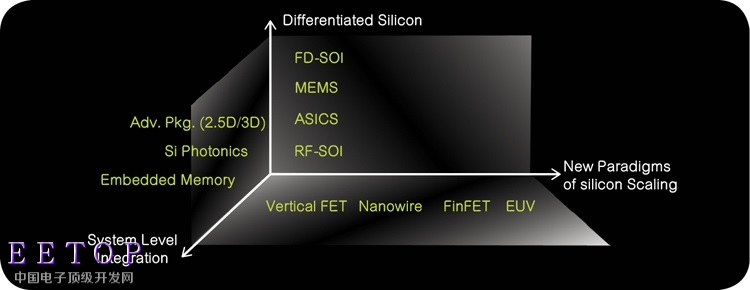

圖4:除了追隨摩爾定律,Globalfoundries技術長Gary Patton認為IC業者應該尋求不同方向的制程與封裝技術創新

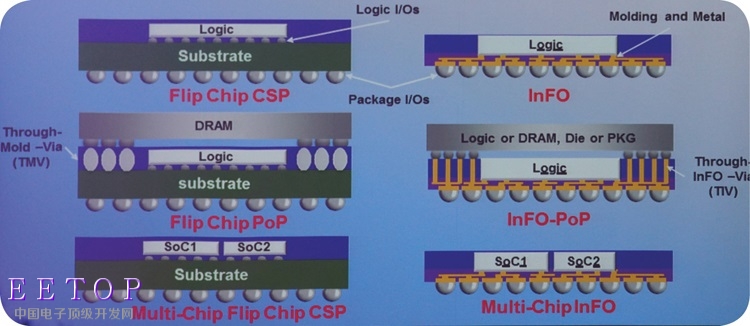

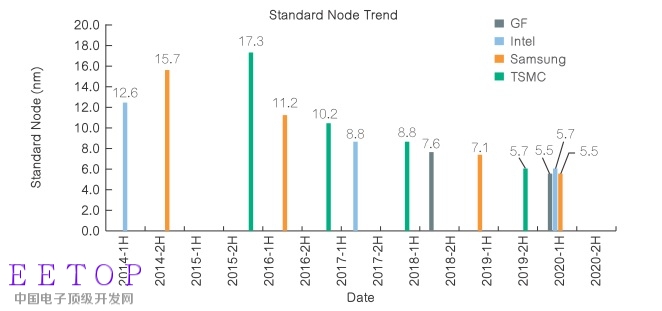

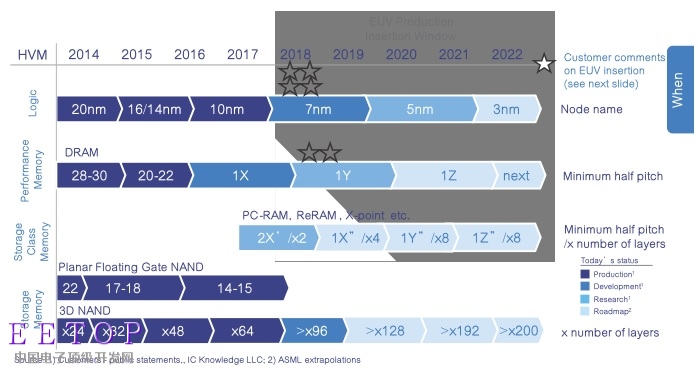

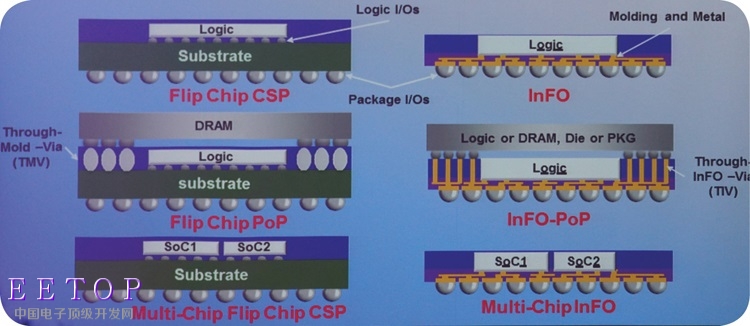

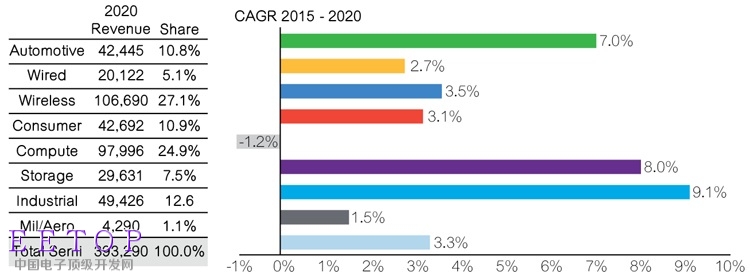

在半導體產業界擁有超過三十年經驗的Patton,在先前向臺灣本地媒體簡報Globalfoundries技術策略時表示,今日市場上有各種各樣新崛起的電子裝置與終端應用,例如行動運算、普適運算(pervasive computing,例如無所不在的連網智能裝置)以及人工智能(AI)、虛擬/擴增實境(AR/VR)... 等等,單一技術并不一定適合所有應用的需求。Patton表示,人工智能、云端運算、高速通訊等應用,目前最尖端的3D晶體管FinFET制程是理想選擇,目前該技術進入14奈米節點量產、已經成熟而且對高階應用有價值;至于對運算性能要求較低、也以較低功率運作的各種嵌入式裝置,例如物聯網設備,其實就不一定要用到最尖端的FinFET制程,否則并不符合成本效益。GlobalFoundries提供的其他技術選項是全空乏絕緣上覆硅(Fully depleted silicon-on-insulator,FD-SOI)制程;Patton指出,該公司準備在2017年量產的22奈米FD-SOI制程,在成本上與成熟的28奈米平面晶體管制程相當,但能達到類似FinFET制程的性能,而且功耗更低、 封裝尺寸更小,也更適合與RF組件的整合。在封裝技術方面,Patton表示在過去一年來,Globalfoundries看到2.5D與3D芯片堆棧的客戶需求有大幅成長的趨勢;目前該公司可提供應用于32~22奈米深度溝槽式晶圓的「智能中介層」(interposer),具備去耦電容,能支持低功率應用的芯片堆棧。在芯片堆棧技術方面,臺灣半導體產業協會(TSIA)理事長、鈺創科技董事長盧超群表示,過去15年來IC產業已經達成了「類似以微觀建筑技術造高樓」的突破,發明3D甚至超越3D的異質性晶粒排列或堆棧方法;再加上半導體廠商在晶圓級封裝技術(WLP)上的研發成果──例如臺積電的整合型扇出(Integrated Fan-out,Info)與整合型扇出-封裝內建封裝技術(InFO-PoP)──將IC制造與封測一體化,會是讓摩爾定律延續更長壽命的關鍵。