Achronix推出Speedcore custom blocks單元塊實現更靈活的定制化功能

2017-10-19 15:58:07 未知為滿足人工智能、5G移動通信、汽車應用、數據中心等計算能力的日益增長對硬件性能提出的更大要求,Achronix 2016年10月份推出了SpeedcoreeFPGA IP,SpeedcoreeFPGA IP可以被嵌入到ASIC或SoC之中,客戶根據所需的邏輯功能、RAM存儲器和DSP資源實現個性化的需求。一年之后,Achronix 宣布為其eFPGA IP解決方案推出Speedcore custom blocks定制單元塊。

Achronix Semiconductor市場營銷副總裁Steve Mensor近日在媒體發布會上表示:“業界領袖對Speedcore custom blocks定制單元塊及其可發揮的潛力倍感興奮,目前與我們合作的公司都在打造下一代異構計算平臺和高帶寬通信系統,他們正在構建高性能的硬件加速器,可以隨著其計算算法的演進而不斷調整。現在,Achronix eFPGA IP產品在添加了Speedcore custom blocks定制單元塊以后,就使其在擁有可編程性的同時還能夠擁有ASIC級的性能以及高片芯面積效率。”

圖1:Achronix Semiconductor市場營銷副總裁Steve Mensor

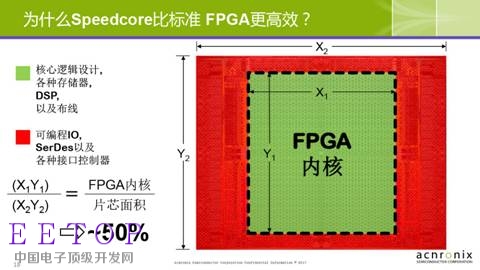

為什么Speedcore比傳統FPGA更高效

讓我們先來回顧一下SpeedcoreeFPGA IP。傳統上,為現實更高的性能,可以通過增加CPU數量來提高頻率,這種技術架構受制于功耗和芯片的大小。為克服增加CPU核帶來的挑戰,行業內提出新的異構計算,簡單的說就是利用外部的硬件加速器去協助CPU對數據的處理,傳統的CPU控制簡單的計算性能,而數據加速器并行處理大量的計算,通過此類組合可以得到更高性能的提升。

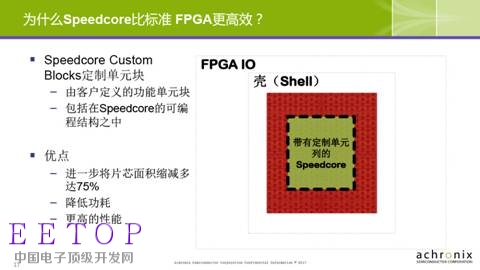

FPGA作為一種硬件加速器,那如何將其集成到一個面積極小的SOC中呢? Steve Mensor說,傳統的FPGA結構中,有30-40%被可編程IO,SerDes以及各種接口控制器等占用,剩下的部分為FPGA核。而Speedcore的高效就在于,第一削減了可編程IO ,第二去除了殼資源,第三便是最近發布的Speedcore custom blocks定制單元塊,可將芯片面積縮減6倍,同時得到更低的功耗和更高的性能。

Speedcore custom blocks單元模塊挑戰更靈活的定制化功能

FPGA技術歷經80年代僅提供基于SRAM的查找表功能,到90年代加入了嵌入式的存儲器功能,2000年用于復雜運算的DSP加入到FPGA架構中,2010年高速傳輸的SerDes和硬化IO協議集成到FPGA中,這些演進的共同點是通用性很強,但卻少定制化,Speedcore custom blocks定制單元塊的推出便是克服挑戰而來。下圖顯示,Speedcore單元塊以列的形式排布,圖中F1和F2列為Speedcore custom blocks定制單元塊,有極高的靈活度,客戶根據自己需求增減功能。

Steve Mensor以三個例子進一步講解了Speedcore custom blocks定制單元塊的優勢。

案例1:通過為矩陣乘法運算優化數字信號處理器(DSP)和存儲單元塊,基于卷積神經網絡(CNN)的YOLO目標識別算法的芯片面積被縮減了超過40%,如下圖。

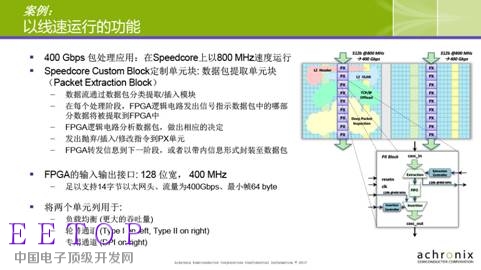

案例2:一個運行在800MHz的400Gbps包處理數據通道的核心功能也可以用Speedcore custom blocks定制單元塊來實現,其可編程邏輯管理分析和控制功能,而今天的FPGA獨立芯片不能為包處理應用提供這么高的數據吞吐量,如下圖。

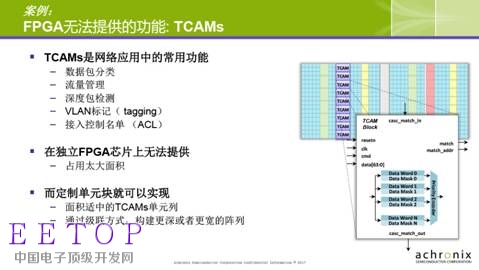

案例3:獨立的FPGA無法提供TCAMs功能。TCAMs是網絡應用中的常用功能,因其占用太大的面積,在獨立的FPGA芯片上無法實現,而通過Speedcore custom blocks定制單元塊的采用,便解決了以上問題,可以通過級聯的方式構建更深或列寬的陣列,如下圖。

ACE工具助力Speedcore custom blocks定制單元塊的應用

那如何去識別哪些模塊可以做成自定義式的呢?Steve Mensor說:“我們通過自己的工具去分析客戶的設計,如果設計中有高頻率的重復使用,我們便認為此設計可以適合自定義模塊。客戶可以通過Achronix所提供的ACE工具進一步為設計方案實現最優的設計。”

ACE工具生成的語言支持設計過程與任何其他FPGA設計相同,全面支持Verilog、 SystemVerilog和VHDL。根據需求,該過程可以被多次迭代,為客戶的系統創建優化的解決方案。

另外,Achronix協助客戶可為Speedcore custom blocks定制單元塊實現定制的界面,通過此介界面可以導入用戶所生成的驗證規則,和各種設計中所需組件的生成。在ACE中還包括一個關鍵路徑分析工具,可以支持客戶分析時序。客戶還可以使用ACE強大的Snapshot嵌入式邏輯分析儀,去創建復雜的觸發器并展示Speedcore內的實時信號。

加上最近發布的 Speedchip,Achronix這家公司基于FPGA的產品線共有三大塊,一是Speedster-獨立FPGA芯片,二是Speedcore-嵌入式FPGA內核,用于芯片集成的IP,三是Speedchip,通過2.5D或MCM方式集成,實現定制化需求。

Achronix 預測2017年第四季度結束后,銷售收入將超過一億美元,值得一提的是Speedcore是此公司增長最快的產品,自2016年第三季度向首批客戶供貨以來,目前為總收入的25%,未來預計此部分將占到總營收的50%。