驍龍835:老子難產,有苦難言

2017-03-16 21:22:02 n315過去后,就可以期待各家手機廠商推出的旗艦新機了……你可能會奇怪,315和手機廠商發布主力新機有什么關系嗎?從以往經驗來看,好像并沒有,但今年比較特殊,因為到目前,拿出自家鎮店旗艦產品的委實不多。在往年,這個時候三星家的Galaxy S新旗艦早就笑傲江湖了,還有小米,記得去年小米5也是在2月24日就早早問世了……今年大家都在等什么呢? 答案很顯然:高通“掉隊”了,驍龍835遲遲沒動靜,手機廠商們也是望眼欲穿……

不過好在,高通已經宣布在3月22日亞洲首秀高通驍龍835處理器,這是個好信號,至少說明這款處理器能拿出來溜溜了,雖然還沒有大規模鋪貨,但至少讓人看到了鋪貨的希望,手機廠商們也有盼頭了。不過此前一度有傳聞三星S8將獨占驍龍835處理器的初期供貨,雖然后來半路殺出的索尼打破了這個傳聞,但考慮三星和高通的關系,其他廠商想要拿貨,那也得是“擼起袖子加油搶”的節奏吧……

當年驍龍810一聲“老子發燒”,讓一眾手機廠商苦不堪言,而現在驍龍835一聲“老子難產”,影響的同樣是不少手機廠商的產品計劃,這里關于廠商自研處理器的重要性和優勢就不說了。其實不僅是驍龍835,同為10nm的像三星Exynos8895、聯發科的Heilo X30等,也好不到哪里去。 2017年是半導體產業10nm工藝爭鋒的關鍵點,大家都遭遇了良率偏低的問題,我們不妨看看,驍龍835們為什么這么難產。

首先,當今半導體產業有芯片代工能力的主要是三家:三星、臺積電、和Intel,而在移動端市場,雖然Intel早前曾放言未來會代工ARM芯片,但目前,仍然是三星和臺積電的天下。2017年,10nm制程是智能手機芯片市場的重要賣點,但根據《電子時報》早前的報道, 目前三星和臺積電的10nm工藝均面臨著良率不理想的難題。

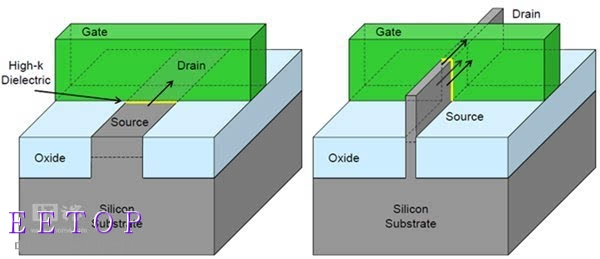

在CPU市場,人們喜愛談論某款CPU采用了XX nm制程工藝,因為這一指標的每一次提升,帶來的都是性能的高漲和功耗的降低,對于芯片產業十分重要。那么這個XX nm背后意味著什么?我們知道,一款CPU中包含上億個晶體管,而一個單獨的晶體管大致結構是這樣的:

▲圖片中給了兩個晶體管,但代表的是兩種技術,都可以作為參考

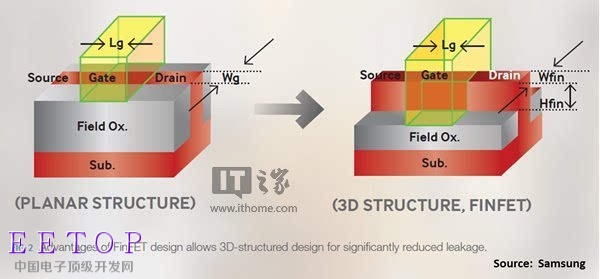

圖中的晶體管結構中,“Gate(柵極)”可以看做是“閘”,主要負責控制兩端Source(源極)和Drain(漏級)的通斷,電流從源極流入漏極,而這時的柵極的寬度決定了電流通過時的損耗,表現出來就是發熱和功耗,寬度越窄,功耗越低。而柵極的寬度(柵長),就是XX nm工藝中的數值。

對于芯片制造商而言,自然是力求柵極寬度越窄越好,不過 當寬度逼近20nm時,柵極對電流控制能力急劇下降,漏電率相應提高,對生產工藝的難度要求也上了一個臺階,例如臺積電在這段時間一度遭遇漏電和產能的問題。而工藝繼續微縮,硅晶體管的尺寸縮小到一定程度(業內認為小于10nm)時會產生量子效應,導致晶體管的特性難以控制,這時候對于芯片的制造生產難度顯然成倍增長。因此,在10nm這個節點上,對三星、臺積電這樣的代工廠而言,考驗和壓力可想而知。

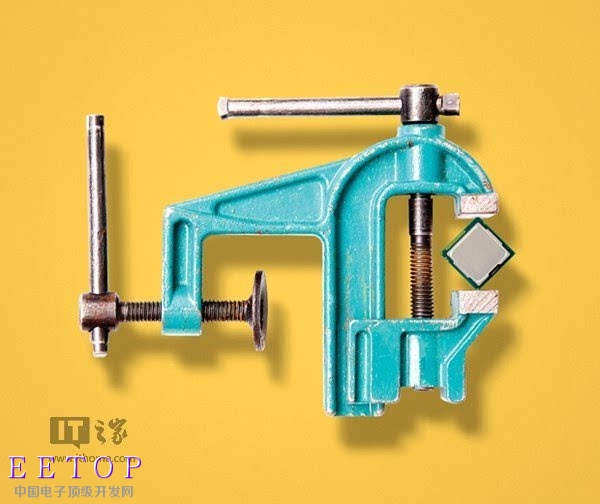

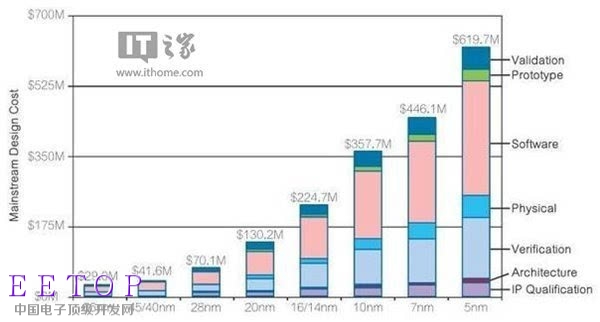

另外,隨著芯片制程來到10nm,設計制造成本的翻漲也令人咋舌。根據市場研究機構IBS的調研報告,10nm制程芯片的設計成本相比14nm,增加接近5成, 持續而巨大的資金投入也是10nm芯片量產的一道難關。

由此可見,對于高通而言,驍龍835的遲到實在不是自己能左右的,在10nm制程半導體廠商爭王奪霸的關鍵時候,代工廠們也在憋著勁看誰能首先克服良率的難關,這種節骨眼上,即便遲到,相信高通也是有苦難言啊。

目前來看,對于非常歡騰的大批國內手機廠商而言, “必須搭載”驍龍835的旗艦手機延遲推出的可能性是非常大的,當然,也不排除有廠商拿到其中一些“體質較差”芯片,帶著“降頻版”的背景搶個“彩頭”。

說到這里你可能會問,對于三星、臺積電們而言,接下來怎么辦呢?誰能夠搶下10nm節點的flag呢?

這就要看誰能夠最先實現新技術的成熟了。例如在20/22nm工藝節點上,Intel引入了3D FinFET技術,把柵極制做成下圖右面的形狀,增大接觸面積,減少柵極寬度的同時保證對電流的控制,后來FinFET技術也被三星臺積電等大范圍使用,而在10nm往后,FinFET技術也要到天花板了,在技術上進行突破創新是必然之選,目前,半導體廠商們正在積極研究FD-SOI(全耗盡絕緣體硅)工藝、硅光子技術、3D堆疊技術等,也投入了巨資,為日后的7nm、甚至5nm做準備,彼此間的競爭也將進一步加劇。

縱觀今年高通驍龍835處理器遲到的背后,實則是半導體產業鏈蛻變前期的陣痛,三星和臺積電之間的競爭已經來到白熱化階段(Intel的10nm制程進展雖然落后,但在工藝上自信更加先進,這里就不展開講了), 也許熬過了這個“難產期”,整個展業會迎來“新生命”。